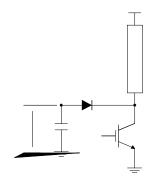

Figure 3. IGBT Switching Test Circuit

٠

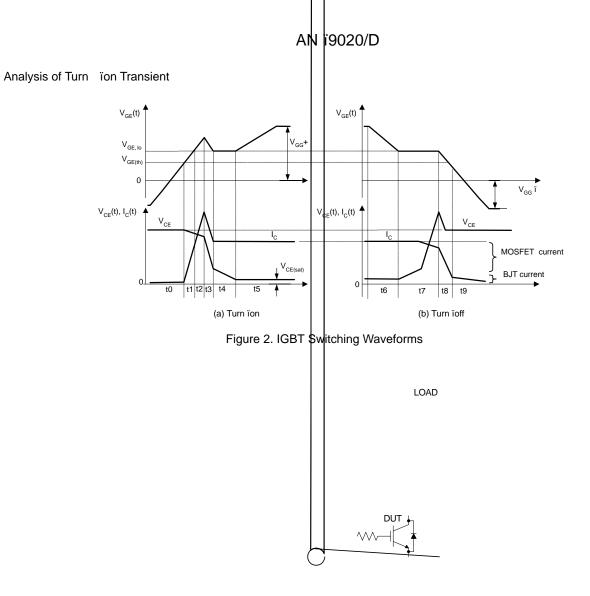

across the diode recovers and increases, while falls, and it falls rapidly as G has small value where that high value. Due to this phenomenon, dv

Effect on State

For the same value of,  $IV_{CE(sat)}$  is inverselyrelated to the value of  $V_{GG+}$ . The smaller the  $V_{G+}$ , the thinner the channel between n+ layer and idrift layer becomes, and the resistance in the hannel increases. Due to the conductivity modulation effect not found in MOSFET, voltage drop in the ni

(FWD) of the IGBT on the opposite side recovers reverse

When the maximum current is actually measured, one Wiring Pattern must beaware that it may be less than the calculated amount due to the falling voltage on the wire and stray inductance. WhenIGBTs are connected in parallel and are operated at a low frequency, low RMS current could lead to a mistaken complacencyHowever, under such situation, the maximum current would be twice as large, since there are 2 IGBTs in operation, and one must be careful that it could lead to the overload of the power supply of the gate drive. Wattage of the R<sub>6</sub> can be decided witthe maximum calculated amount of current.

#### Gate Drive Layout Considerations

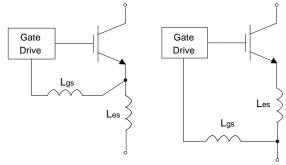

Effect of Gate Line Inductance on the Induced Tom

Possibility of induced turn ion is greater, as the gate drive impedance is increased during twom and turrioff current flows through Rto reduce the charging current of  $C_{qer}$  which causes the amount of increase ieta reduce. supply must be minimized, and Bhould be kept at minimum.

# Power Source Stabilizing Capacitor

During IGBT switching, current flows to the gate, and at thattime, supply voltage of the gate circuit can oscillate. As a result, the gate drive loss can exceed the designed amount, or it could reduce the short circuit capability. In such case, it is advised to keep PCB pattern wide and flat and use enough capacitor for supply voltage stability.

# **Isolation Problem**

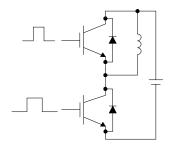

In half bridge topology and similar systems, the upper IGBT gate drive circuits must insulated from the bottom IGBT circuits. The control board and the gate drive must also beinsulated because the upper IGBT emitter free floats as the IGBT switches. As the power DC voltage rises, the

At the time of switching, voltage is induced across the insulating voltage should also rise accordingly. In general, stray inductance of the power circuit because of di/dt from the insulating voltage should be at least twice the rated the main current. When control signals from the gate drive voltage for the IGBT. Inaddition, care has to be taken with and the same path as the main current are used, gate voltage the noise that comes about from insulating interface. decreases during turon, and voltage is added to the gate Immunity tonoise differs depending on the how and where the circuits lines are placed, so wiring and placement should such, it is better not to share stray inductance between be designed to minimize parasitic capacitance. Parasitic control emitter terminal and power emitter terminal. As capacitance should be minimized to reduced to such, control emitter terminal and power emitter terminal using a common transformer to provide current to both the upper and the lower gate drive, the wire must be wound to speed and switching loss. minimize combined capacitance. In using optoupler, the Voltage oscillation, slow gate voltage rise, noise opto icoupler must have insulating capacity with high immunity deterioration, gate voltage reduction, falling gate

commonmode voltage and transient noise immunity. Upper and lower, or different types of gate leads of the gate drive layout. These can be solved with designs to reduce stray must not be wound together.

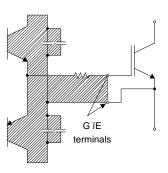

Figure 6. Gate Drive Pattern 6

The final pushipull wiring pattern should be short and thick, and if a directonnection between the gate drive and transient due to stray inductance from the line connected the IGBT is not possible, then gate wire and the emitter wire with the gate. As gate impedance becomes smaller, more ould be twisted to reduce stray inductance. In addition, if the area of the loop that encompasses the final ipush stage, the power source pattern, And GiE terminals of In order to prevent this, leakage inductance from DC power the IGBT is minimized as shown in Figure 6, effect on the  $V_{GE}$ , from di/dt could be minimized when  $V_{GE}$  is injected.

**Common Emitter Problems**

Figure 7. Common Emitter

inductance and stray resistance such as making patterns short and thick. In addition, attention must be paid to the power circuit layout to minimize stray inductance. For example the area of the closed loop must be minimized with DC link capacitor, load, power output, hällfidge leg and snubbers in the case of inverter, and in the case of resistive load, line to the load should be twisted to reduce the stray inductance of the power circuit, while snubber should be strengthened depending on the amount of öxcetage for inductive load. As the frequency increases, voltage could change due to slowing response of the dc link capacitor, so high ispeed electrolyst cap for inverter should be used, and capacitor with better characteristics such as film capacitor should be inserted in the main cap in parallel.

#### Conclusion

We have examined some issues to consider in the gate

IGBT's latch"up. It is possible to obtain short circuit time with short circuit testing of different products from many companies. In general, short circuit time becomes longer with high saturation voltage and  $\mathcal{Y}_{(sat)}$  (In measuring  $\mathcal{Y}_{E}$  (sat) gate voltage should be enough for the minimum value of  $V_{CE(sat)}$  and that level must be maintained during fault test.)

# Types of Short Circuit

Short circuit can happen while IGBT's normal function. Short circuit can be divided into two different types. The first is shortïcircuiting when the device was in on state, which is called "fault under load" and the second is a circumstance when the device turns on under short circuit, which is called "hard switch fault".

Type I. Fault Under Load (FUL)

Figure 9. Fault Under Load Test Circuit

Figure 10. Fault Under Load Waveform

Fault under load (FUL) is a situation where shicincuit takes place when the device is in on state, so this Vow

#### Short Circuit Protection

We have discussed types of short circuits, and several ways toprevent short circuits have been reviewed. However, methodsmentioned above are not fundame**mtalys** to deal with shortcircuit, so there has to be a way to safely turn off the device when it short circuits.

### Protecting Against Overcurrent Condition

Overïcurrent iswhen more than the rated current flows through the system, and it can be classified into boad. shortïcircuit, turnïon overïcurrent. In traditional applications, overcurrent is possible in several cases. Generally,over ïcurrent from overïload comes from inrush current, filter inrush and a rapid change in load during beginning of operation of electrical devices. In this case, we can only rely on short circuit capability of the device. Overïload, ingeneral, lasts much longer than the IGBT's short circuit endurance time. As such, other methods must be sought to remove the overload. Closed loop control moderates the timing signal of the gate drive pulse, to modifies the time of switching, and this is used to keep the currentoutput at a determined level. Response control of the controlloop would have to be set to the rate of changes in the currentand pace of the electrical devices or filter inductance. Protection from overcurrent due to shortcircuit is different from turnioff over current. In the following sections, protectiofrom shortïcircuit would be discussed.

# Protecting Against Short Circuit Current Condition

In the overload situations mentioned above, removing the closed loop does not considerably shorten the life of the IGBT. On the other hand, short circuit provides worse condition for the life of the device than overload or the over ïcurrent at turn ïon, and there are ground faults, terminalïto ïterminal faults. Such short circuit current bypasses the electrical devices or filter inductance and increasesapidly for IGBT to flow Conventional PWM loop controlspower output, but it has no control over this type of fault. At the beginning of the faulthe IGBT must with stand with its own short circuit capability, and protection mechanism receives the fault signal to reduce the gate voltage while IGBT withstands the short circuit. However, if the fault disappears while during IGBT's endurance time, then the IGBT must continue to function and must not turn off unnecessary devices or turn off the entire system. The most notable is the IGBT tuinon overïcurrent due to the reverse recovery current of the diode. As such, the protection circuit must be designed to return the circuit to normal operation if the fault is removed before the IGBT shuts down the system.

When conduction time increases, the border of SOA (SCSOA) decreases. Junction temperature increases

Figure 15. Short ïcircuit Sensing Circuit using De ïsaturation Method

### Snubber Circuit

#### Types of Snubber Circuits and their Features

Snubber circuit is a supplementary circuit used in the converter circuit to reduce stress put on the power semiconductorThe ultimate goal of the snubber circuit is to improve the transient waveform. The snubber circuit suppresses ovecurrent or overvoltage or improves dv/dt and di/dt to ease the transient waveform to reduce stress on the device. There are many uses for snubber circuits, but this discussionwill center on its ability to suppress ovecurrent at turnïoff.

Snubber circuit can be divided into those connected in between the DC power supply bus and ground, and those connected to each IGBT. The first types of circuits include RC snubber circuits, charge and discharge RCD snubber circuits and discharge suppressing RCD snubber circuits, and the second type includes C snubber circuits and RCD snubber circuits. The followingre detailed descriptions of each snubber circuit.

# **RC Snubber Circuit**

This snubber circuit ieffective in turnïoff surge voltage and is suitable for chopper circuits. It is also effective for oscillationby parasitic reactance and dv/dt noise. However, when itis applied in large capacity IGBT, resistance for the snubber must be set lodvue to dissipation dfieat, so it has the disadvantage of worsening loading conditions at turn ïon. Lossat snubber itself is quite large, so it is not suitable for high frequency. In very large capacity IGBT circuit, it isbetter to use small snubber "RC snubber circuit" along with themain snubber "dischargeuppressing RCD snubber circuit." When used together, it helps parasitic oscillation control of the main snubber loop. Main applicationsinclude arc welder and switching power supply.

# Charge and Discharge RCD Snubber Circuit

This snubber suppresses owworltage at turnoff to reduce switchingosses at turnoff, and its effectiveness in surge voltage suppression is about average. The snubber capacitoris completely dischgred at turnon, and it is fully recharged at turnoff. Unlike the dischargesuppressing RCD snubber circuit below which acts as a clamp, this circuit of4e increases to present problems in controlling öveltage. In such large current applications, dischäsgepressing References

- Malay Trivedi and Krishna Shenai, "Failure Mechanism of IGBT's Under ShoitCircuit and Clamped Inductive Switching StrestEE Trans. Power Electronicsvol. 14, no. 1, pp. 108/16, 1999.

- [2] Rahul S. Chokhawala and Saed Sobhani, "Switching Voltage Transient Protection Schemes for High ïCurrent IGBT Modules", IEEE Trans. Industry Applications