#### Description

The PCA9554 is a CMOS device that provides 8-bit parallel input/output port expansion for  $I^2C$  and SMBus compatible applications. This I/O expander provides a simple solution in applications where additional I/Os are needed: sensors, power switches, LEDs, pushbuttons, and fans.

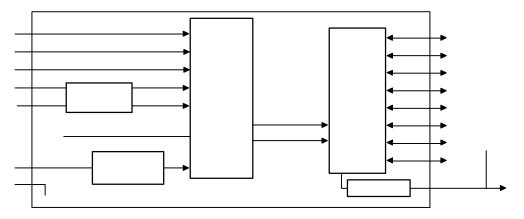

The PCA9554 consist of an input port register, an output port

Figure 1. Block Diagram

| Symbol            | Parameter              | Conditions                                                                                         | Min | Тур  | Max  | Unit |  |

|-------------------|------------------------|----------------------------------------------------------------------------------------------------|-----|------|------|------|--|

| SUPPLIES          |                        | -                                                                                                  |     |      |      |      |  |

| V <sub>CC</sub>   | Supply voltage         |                                                                                                    | 2.3 | -    | 5.5  | V    |  |

| I <sub>CC</sub>   | Supply current         | Operating mode; V <sub>CC</sub> = 5.5 V;<br>no load; f <sub>SCL</sub> = 100 kHz                    | -   | 104  | 175  | μΑ   |  |

| I <sub>stbl</sub> | Standby current        | Standby mode; $V_{CC}$ = 5.5 V; no load; $V_I$ = $V_{SS}$ ; f <sub>SCL</sub> = 0 kHz; I/O = inputs | -   | 550  | 700  | μΑ   |  |

| I <sub>stbh</sub> | Standby current        | Standby mode; $V_{CC}$ = 5.5 V; no load; $V_I$ = $V_{CC}$ ; f <sub>SCL</sub> = 0 kHz; I/O = inputs | -   | 0.25 | 1    | μΑ   |  |

| V <sub>POR</sub>  | Power-on reset voltage | No load; $V_I = V_{CC}$ or $V_{SS}$                                                                | -   | 1.5  | 1.65 | V    |  |

SCL, SDA,  $\overline{\text{INT}}$

V

|                           |                                            | Stand | ard I <sup>2</sup> C | Fast I <sup>2</sup> C |     |       |

|---------------------------|--------------------------------------------|-------|----------------------|-----------------------|-----|-------|

| Symbol                    | Parameter                                  | Min   | Max                  | Min                   | Max | Units |

| F <sub>SCL</sub>          | Clock Frequency                            |       | 100                  |                       | 400 | kHz   |

| t <sub>HD:STA</sub>       | START Condition Hold Time                  | 4     |                      | 0.6                   |     | μs    |

| t <sub>LOW</sub>          | Low Period of SCL Clock                    | 4.7   |                      | 1.3                   |     | μS    |

| t <sub>HIGH</sub>         | High Period of SCL Clock                   | 4     |                      | 0.6                   |     | μS    |

| t <sub>SU:STA</sub>       | START Condition Setup Time                 | 4.7   |                      | 0.6                   |     | μs    |

| t <sub>HD:DAT</sub>       | Data In Hold Time                          | 0     |                      | 0                     |     | μs    |

| t <sub>SU:DAT</sub>       | Data In Setup Time                         | 250   |                      | 100                   |     | ns    |

| t <sub>R</sub> (Note 9)   | SDA and SCL Rise Time                      |       | 1000                 |                       | 300 | ns    |

| t <sub>F</sub> (Note 9)   | SDA and SCL Fall Time                      |       | 300                  |                       | 300 | ns    |

| t <sub>SU:STO</sub>       | STOP Condition Setup Time                  | 4     |                      | 0.6                   |     | μS    |

| t <sub>BUF</sub> (Note 9) | Bus Free Time Between STOP and START       | 4.7   |                      | 1.3                   |     | μS    |

| t <sub>AA</sub>           | SCL Low to Data Out Valid                  |       | 3.5                  |                       | 0.9 | μs    |

| t <sub>DH</sub>           | Data Out Hold Time                         | 100   |                      | 50                    |     | ns    |

| T <sub>i</sub> (Note 9)   | Noise Pulse Filtered at SCL and SDA Inputs |       | 100                  |                       | 100 | ns    |

| Table 5. A.C. CHARACTERISTICS (V <sub>CC</sub> = 2.3 V to | 5.5 V; $T_A = -40^{\circ}C$ to +85°C, unless otherwise specified.) (Note 8) |

|-----------------------------------------------------------|-----------------------------------------------------------------------------|

|-----------------------------------------------------------|-----------------------------------------------------------------------------|

| Symbol          | Parameter             | Min | Max | Units |

|-----------------|-----------------------|-----|-----|-------|

| PORT TIMING     |                       |     |     |       |

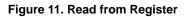

| t <sub>PV</sub> | Output Data Valid     |     | 200 | ns    |

| t <sub>PS</sub> | Input Data Setup Time | 100 |     | ns    |

| t <sub>PH</sub> | Input Data Hold Time  | 1   |     | μs    |

| INTERRUPT TIM   | ING                   |     |     |       |

| t <sub>IV</sub> | Interrupt Valid       |     | 4   | μs    |

4

μs

Interrupt Reset

8. Test conditions according to "AC Test Conditions" table.

9. This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.

#### Table 6. A.C. TEST CONDITIONS

t<sub>IR</sub>

| Input Rise and Fall time      | ≤ 10 ns                                                                 |

|-------------------------------|-------------------------------------------------------------------------|

| CMOS Input Voltages           | 0.2 $V_{CC}$ to 0.8 $V_{CC}$                                            |

| CMOS Input Reference Voltages | 0.3 V <sub>CC</sub> to 0.7 V <sub>CC</sub>                              |

| TTL Input Voltages            | 0.4 V to 2.4 V                                                          |

| TTL Input Reference Voltages  | 0.8 V, 2.0 V                                                            |

| Output Reference Voltages     | 0.5 V <sub>CC</sub>                                                     |

| Output Load: SDA, INT         | Current Source $I_{OL}$ = 3 mA; $C_L$ = 100 pF                          |

| Output Load: I/Os             | Current Source: $I_{OL}/I_{OH} = 10 \text{ mA}$ ; $C_L = 50 \text{ pF}$ |

## **Functional Description**

The PCA9554's general purpose input/output (GPIO) peripherals provide up to eight I/O ports, controlled through an I<sup>2</sup>C compatible serial interface.

The PCA9554 supports the I<sup>2</sup>C Bus data transmission protocol. This I<sup>2</sup>C Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. The transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The PCA9554 operates as a Slave device. Both the Master device and Slave device can operate as either transmitter or receiver, but the Master device controls which mode is activated.

### I<sup>2</sup>C Bus Protocol

The features of the I<sup>2</sup>C bus protocol are defined as follows:

- 1. Data transfer may be initiated only when the bus is not busy.

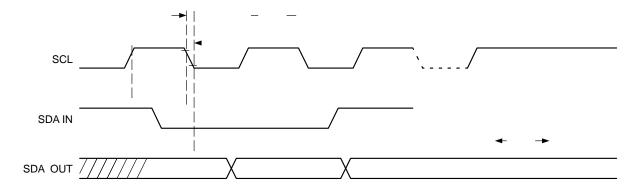

- 2. During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition (Figure 6).

### **START and STOP Conditions**

The START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The PCA9554 monitors the SDA and SCL lines and will not respond until this condition is met.

A LOW to HIGH transition of SDA when SCL is HIGH

### Acknowledge

After a successful data transfer, each receiving device is required to generate an acknowledge. The acknowledging device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data. The SDA line remains stable LOW during the HIGH period of the acknowledge related clock pulse (Figure 6).

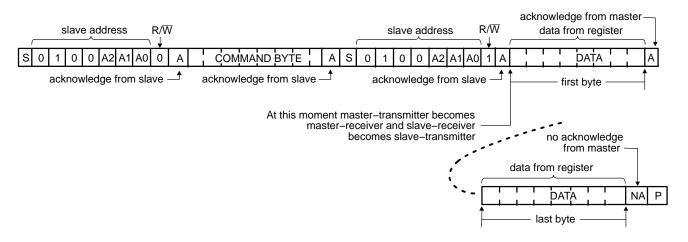

The PCA9554 responds with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation, it responds with an acknowledge after receiving each 8-bit byte.

When the PCA9554 begins a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowledge, the PCA9554 will continue to transmit data. If no acknowledge Is sent by the Master, the device terminates data transmission and waits for a STOP condition. The master must then issue a STOP condition to return the PCA9554 to the standby power mode and place the device in a known state.

#### **Registers and Bus Transactions**

The PCA9554 consists of an input port register, an output port register, a polarity inversion register and a configuration register. Table 7 shows the register address table. Tables 8 to 11 list Register 0 through Register 3 information.

#### Table 7. REGISTER COMMAND BYTE

| Command<br>(hex) | Protocol        | Function                    |

|------------------|-----------------|-----------------------------|

| 0x00             | Read byte       | Input port register         |

| 0x01             | Read/write byte | Output port register        |

| 0x02             | Read/write byte | Polarity inversion register |

| 0x03             | Read/write byte | Configuration register      |

The command byte is the first byte to follow the device address byte during a write/read bus transaction. The register command byte acts as a pointer to determine which register will be written or read.

The input port register is a read only port. It reflects the incoming logic levels of the I/O pins, regardless of whether the pin is defined as an input or an output by the configuration register. Writes to the input port register are ignored.

| bit     | I <sub>7</sub> | ۱ <sub>6</sub> | $I_5$ | I <sub>4</sub> | I <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> |

|---------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|

| default | 1              | 1              | 1     | 1              | 1              | 1              | 1              | 1              |

#### Table 9. REGISTER 1 – OUTPUT PORT REGISTER

| bit     | 0 <sub>7</sub> | O <sub>6</sub> | O <sub>5</sub> | O <sub>4</sub> | O <sub>3</sub> | O <sub>2</sub> | O <sub>1</sub> | O <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| default | 1              | 1              | 1              | 1              |                |                |                |                |

The output port register sets the outgoing logic levels of the I/O ports, defined as outputs by the configuration register. Bit values in this register have no effect on I/O pins defined as inputs. Reads from the output port register reflect the value that is in the flip–flop controlling the output, not the actual I/O pin value.

The polarity inversion register allows the user to invert the polarity of the input port register data. If a bit in this register is set ("1") the corresponding input port data is inverted. If a bit in the polarity inversion register is cleared ("0"), the original input port polarity is retained.

The configuration register sets the directions of the ports. Set the bit in the configuration register to enable the corresponding port pin as an input with a high impedance output driver. If a bit in this register is cleared, the corresponding port pin is enabled as an output. At power–up, the I/Os are configured as inputs with a weak pull–up resistor to  $V_{\rm CC}$ .

Data is transmitted to the PCA9554's registers using the write mode shown in Figure 9 and Figure 10.

The PCA9554's registers are read according to the timing diagrams shown in Figure 11 and Figure 12. Once a command byte has been sent, the register which was addressed will

### Power-On Reset Operation

When the power supply is applied to  $V_{CC}$  pin, an internal power–on reset pulse holds the PCA9554 in a reset state until  $V_{CC}$  reaches  $V_{POR}$  level. At this point, the reset

condition is released and the internal state machine and the PCA9554's registers are initialized to their default state.

Figure 12. Read Input Port Register

TSSOP16, 4.4x5 CASE 948AN ISSUE O

DATE 19 DEC 2008

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi