U U

onse 1

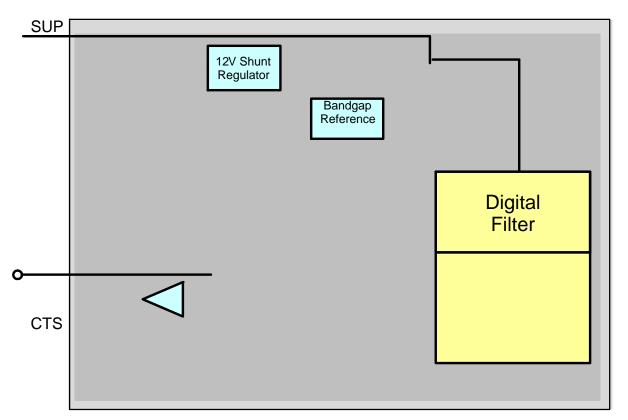

Figure 1. Simplified Block Diagram

#### **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                         | Symbol              | Value                                                           | Unit |

|--------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------|------|

| Supply Voltage Range                                                           | Vs                  | 13.5                                                            | V    |

| Supply Current                                                                 | Is                  | 10                                                              | mA   |

| Input Voltage Range (Note 3)                                                   | V <sub>in</sub>     | -0.3 to 3.6                                                     | V    |

| Output Voltage Range                                                           | V <sub>out</sub>    | -0.3 to 3.6 V or (V <sub>in</sub> + 0.3),<br>whichever is lower | V    |

| Maximum Junction Temperature                                                   | T <sub>J(max)</sub> | 140                                                             | °C   |

| Storage Temperature Range                                                      | TSTG                | -65 to 150                                                      | °C   |

| ESD Capability, Human Body Model (Note 4)                                      | ESD <sub>HBM</sub>  | 2                                                               | kV   |

| ESD Capability, Charge Device Model (Note 4)                                   | ESD <sub>CDM</sub>  | 500                                                             | V    |

| Lead Temperature Soldering Reflow (SMD Styles Only), Pb–Free Versions (Note 5) | T <sub>SLD</sub>    | 260                                                             | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Functional operation above the Recommended Operating Conditions is not implied. Extended

- Exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 4. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per JS-001-2012 ESD Charge Device Model tested per JESD22-C101-F

- Latchup Current Maximum Rating: ≤ 100 mA per JEDEC standard: JESD78D

- 5. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

#### **Table 3. THERMAL CHARACTERISTICS**

| Rating                                                                                         | Symbol          | Value | Unit |

|------------------------------------------------------------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, QFN16, 3x3.3 mm (Note 6) Thermal Resistance, Junction–to–Air (Note 7) | $R_{\theta JA}$ | 64    | °C/W |

- 6. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 7. Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

| Table 4. OPERATING RANGES (Unless otherwise noted, I <sub>SUP</sub> |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

### **APPLICATIONS INFORMATION**

LOAD

pin will be enabled and the CT current (set at 8 mA, R2) will be verified for two half cycles. If a ST cycle fails due to a low GF detection or a GF signal greater than 30 mA, the LED blinking logic will be enabled. Another ST cycle will occur in one minute. If seven consecutive ST cycles fail the SCR will be enabled. If a ST cycle passes before the 7 consecutive cycle counter, the ST logic will be reset and a ST cycle will occur in 17 minutes.

The CT is biased at 1.65 volts. The sense amplifier monitors the ground fault current. This current is converted to a voltage level at the CTO pin which is the input to the ADC (IDF pin). The resistor R8 sets the GF threshold per the following equation:

$$I_{diff} = \frac{0.203 \times CT_{1} \times \left(R_{CT1} + R_{1} + 2\pi f_{AC}L_{CT1}\right)}{R_{8} \times \left(R_{CT1} + 2\pi f_{AC}L_{CT1}\right)} \text{ (eq. 1)}$$

$CT_1$  = Turns ratio of differential CT

R<sub>CT1</sub> = DC winding resistance of differential CT

$f_{AC} = AC$  mains frequency

$L_{CT1}$  = Inductance of differential CT

The ground fault detection circuit has different levels of time delay before the SCR is enabled:

| ≤ 125 ms     |

|--------------|

| ≤ 95 ms      |

| ≤ 75 ms      |

| ≤ 60 ms      |

| $\leq$ 50 ms |

| ≤ 40 ms      |

| ≤ 35 ms      |

| ≤ 25 ms      |

| $\leq$ 20 ms |

|              |

If a very high GF occurs and a greater than 200 mV signal occurs across the CT for greater than 1.4 ms, the SCR will be enabled immediately.

Note that the above equation is for an ideal CT. In practice, the GF threshold can be  $\pm$  30% different and should be empirically set.

When the PTT pin is enabled for greater than 64 ms and

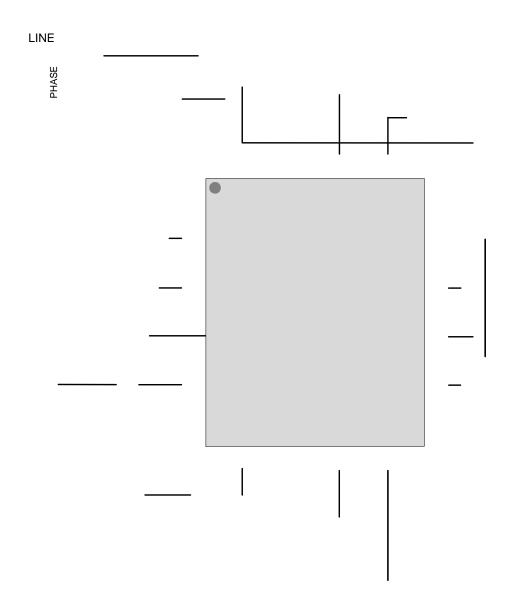

#### QFN16 3x3, 0.5P CASE 485FQ ISSUE B

DATE 12 JUL 2022

# RECOMMENDED MOUNTING FOOTPRI

GENERIC

MARKING DIAGRAM\*

XXXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.