# F -C V D SD R F

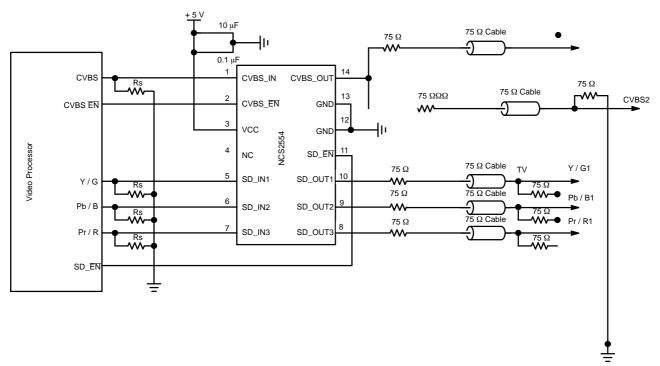

The NCS2554 is a 4-channel high speed video driver with 6th order Butterworth Reconstruction filters on each channel. A first set of 3-channel has Standard Definition (SD) filters, one per channel. A fourth channel offers an extra filter driver for driving Cvbs-type video signal. The NCS2554 is in fact a combination of a triple SD video driver for YPbPr plus a single Cvbs video driver.

It is designed to be compatible with Digital-to-Analog Converters (DAC) embedded in most video processors.

To further reduce power consumption, 2 enable pins are provided one for the triple driver and another one for the single driver. All channels can accept DC- or AC- 0.2

- Integrated Level Shifter

- AC- or DC-Coupled Inputs and Outputs

- Low Quiescent Current

- Shutdown Current 42 µA Typical (Disabled)

- Each channel Capable to Drive 2 by 150 Ω Loads

- Wide Operating Supply Voltage Range: +4.7 V to +5.3 V

- Robust ESD protection 8 kV

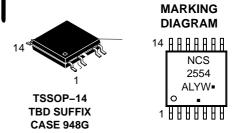

- TSSOP-14 Package

- This is a Pb-Free Device

#### **Typical Application**

- Set Top Box Decoder

- DVD Player / Recorder

- SDTV

http://onsemi.com

NCS2554 = Specific Device Code A = Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ Pb-Free Package

####

#### ORDERING INFORMATION

| Device        | Package               | Shipping <sup>†</sup> |  |  |

|---------------|-----------------------|-----------------------|--|--|

| NCS2554DTBR2G | TSSOP-14<br>(Pb-Free) | 2500 /<br>Tape & Reel |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **MAXIMUM RATINGS**

| Rating                                    | Symbol           | Value                       | Unit |

|-------------------------------------------|------------------|-----------------------------|------|

| Power Supply Voltages                     | V <sub>CC</sub>  | $-0.3 \le V_{CC} \le 5.5$   | Vdc  |

| Input Voltage Range                       | V <sub>I</sub>   | $-0.3 \le V_{I} \le V_{CC}$ | Vdc  |

| Input Differential Voltage Range          | V <sub>ID</sub>  | $-0.3 \le V_{I} \le V_{CC}$ | Vdc  |

| Output Current (Indefinitely) per Channel | I <sub>O</sub>   | 40                          | mA   |

| Maximum Junction Temperature (Note 2)     | T <sub>J</sub>   | 150                         | °C   |

| Operating Ambient Temperature             | T <sub>A</sub>   | -40 to +85                  | °C   |

| Storage Temperature Range                 | T <sub>stg</sub> | -60 to +150                 | °C   |

| Thermal Resistance, Junction-to-Air       | $R_{	heta JA}$   | 125                         | °C/W |

**DC ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = +5.0 V,  $R_{source}$  = 37.5  $\Omega$ ,  $T_A$  = 25°C, inputs AC–coupled with 0.1  $\mu$ F, all outputs AC–coupled with 220  $\mu$ F into 150  $\Omega$  referenced to 400 kHz; unless otherwise specified)

| Symbol          | Characteristics                               | Conditions                              | Min | Тур | Max      | Unit     |  |  |

|-----------------|-----------------------------------------------|-----------------------------------------|-----|-----|----------|----------|--|--|

| POWER SUPPLY    |                                               |                                         |     |     |          |          |  |  |

| V <sub>CC</sub> | Supply Voltage Range                          |                                         | 4.7 | 5.0 | 5.3      | V        |  |  |

| I <sub>CC</sub> | Supply Current                                | SD Channels Selected + C <sub>vbs</sub> |     | 40  | 55       | mA       |  |  |

| I <sub>SD</sub> | Shutdown Current (CVBS_EN and SD_EN High)     |                                         |     | 42  | 60       | μΑ       |  |  |

| DC PERFORMANCE  |                                               |                                         |     |     |          |          |  |  |

| Vi              | Input Common Mode Voltage Range               |                                         | GND |     | 1.4      | $V_{PP}$ |  |  |

| V <sub>IL</sub> | Input Low Level for the Control Pins (2, 11)  |                                         | 0   |     | 0.8      | V        |  |  |

| V <sub>IH</sub> | Input High Level for the Control Pins (2, 11) |                                         | 2.4 |     | $V_{CC}$ | V        |  |  |

| R <sub>pd</sub> | Pulldown Resistors on Pins CVBS_EN and SD_EN  |                                         |     | 250 |          | kΩ       |  |  |

| OUTPUT          | CHARACTERISTICS                               |                                         |     |     |          |          |  |  |

| V <sub>OH</sub> | Output Voltage High Level                     |                                         |     | 2.8 |          | V        |  |  |

| V <sub>OL</sub> | Output Voltage Low Level                      |                                         |     | 200 |          | mV       |  |  |

|                 | _                                             |                                         |     |     |          |          |  |  |

AC ELECTRICAL CHARACTERISTICS FOR STANDARD DEFINITION CHANNELS (pin numbers (1, 14) (5, 10), (6, 9), (7, 8)) ( $V_{CC}$  = +5.0 V,  $V_{in}$  = 1  $V_{PP}$ ,  $R_{source}$  = 37.5  $\Omega$ ,  $T_A$  = 25°C, inputs AC–coupled with 0.1  $\mu$ F, all outputs AC–coupled with 220  $\mu$ F into 150  $\Omega$  referenced to 400 kHz; unless otherwise specified)

| Symbol                  | Characteristics                       | Conditions                              | Min        | Тур        | Max | Unit |

|-------------------------|---------------------------------------|-----------------------------------------|------------|------------|-----|------|

| MTH<br>A <sub>VSD</sub> | Voltage Gain                          | V <sub>in</sub> = 1 V – All SD Channels | 5.8        | 6.0        | 6.2 | dB   |

| BW <sub>SD</sub>        | Low Pass Filter Bandwidth (Note 4)    | –1 dB<br>–3 dB                          | 5.5<br>6.5 | 7.2<br>8.0 |     | MHz  |

| A <sub>RSD</sub>        | Stop-band Attenuation (Notes 4 and 5) | @ 27 MHz                                | 43         | 50         |     | dB   |

| dG <sub>SD</sub>        | Differential Gain Error               |                                         |            | 0.7        |     | %    |

| $d\Phi_{SD}$            | Differential Phase Error              |                                         |            | 0.7        |     | •    |

# TYPICAL CHARACTERISTICS

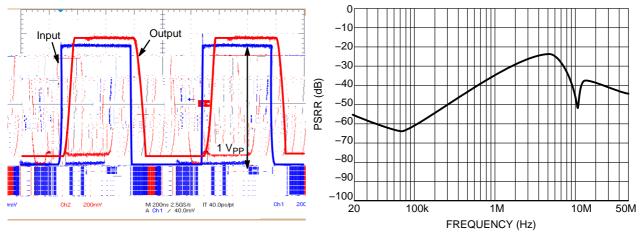

$V_{CC}$  = +5.0 V,  $V_{in}$  = 1  $V_{PP},\,R_{source}$  = 37.5  $\Omega$

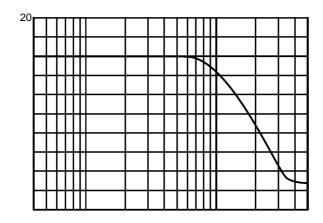

#### **TYPICAL CHARACTERISTICS**

$V_{CC}$  = +5.0 V,  $V_{in}$  = 1  $V_{PP}$ ,  $R_{source}$  = 37.5  $\Omega$ ,  $T_A$  = 25°C, Inputs AC–coupled with 0.1  $\mu$ F, All Outputs AC–coupled with 220  $\mu$ F into 150  $\Omega$  Referenced to 400 kHz; unless otherwise specified

Figure 9. SD Large Signal Response

Figure 10. SD  $V_{CC}$  PSRR vs. Frequency

Figure 11. SD Frequency Response and Group Delay

#### **APPLICATIONS INFORMATION**

The NCS2554 quad video driver has been optimized for Standard video applications covering the requirements of the standards Composite video (Cvbs), S–Video, Component Video (480i/525i, 576i/625i) and related (RGB). The three SD channels have 8 MHz filters for covering standard definition—like video applications.

In the regular mode of operation each channel provides an internal voltage—to—voltage gain of 2 from input to output. This effectively reduces the number of external components required as compared to discrete approached implemented with stand alone op amps. An internal level shifter is

employed shifting up the output voltage by adding an offset of 200 mV. This prevents sync pulse clipping and allows DC–coupled output to the 150  $\Omega$  video load. In addition, the NCS2554 integrates a 6<sup>th</sup> order Butterworth filter for each. This allows rejection of the aliases or unwanted over-sampling effects produced by the video DAC. Similarly for the case of DVD recorders which use an ADC, this anti–aliasing filter (reconstruction filter) will avoid picture quality issue and will aide filtration of parasitic signals caused by EMI interference.

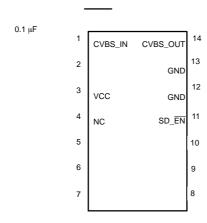

Figure 14. AC-Coupled Configuration at the Input and Output

Figure 17. NCS2554 Driving 2 SCARTS Simultaneously