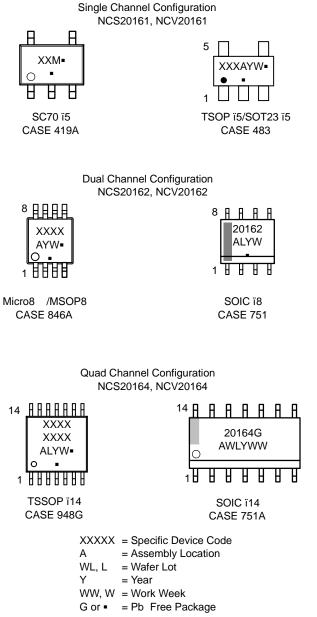

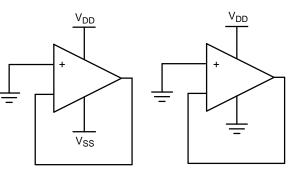

#### MARKING DIAGRAMS

(Note: Microdot may be in either location)

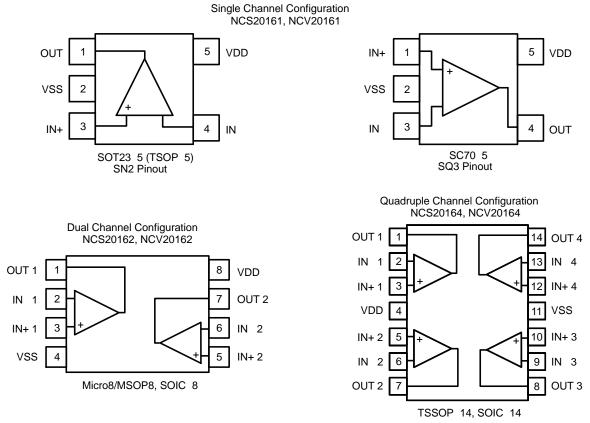

Figure 1. Pin Connections

#### ORDERING INFORMATION

| Device*          | Configuration | Automotive | Marking | Package        | Shipping <sup>†</sup> |

|------------------|---------------|------------|---------|----------------|-----------------------|

| NCS20161SQ3T2G** | Single        | No         | TBD     | SC70           | 3000 / Tape and Reel  |

| NCS20161SN2T1G** |               |            | TBD     | SOT23 5/TSOP 5 | 3000 / Tape and Reel  |

| NCV20161SQ3T2G** |               | Yes        | TBD     | SC70           | 3000 / Tape and Reel  |

| NCV20161SN2T1G** |               |            | TBD     | SOT23 5/TSOP 5 | 3000 / Tape and Reel  |

| NCS20162DMR2G**  | Dual          | No         | TBD     | Micro8/MSOP8   | 4000 / Tape and Reel  |

| NCS20162DR2G     |               |            | 20162   | SOIC 8         | 2500 / Tape and Reel  |

| NCV20162DMR2G**  |               | Yes        | TBD     | Micro8/MSOP8   | 4000 / Tape and Reel  |

| NCV20162DR2G     |               |            | 20162   | SOIC 8         | 2500 / Tape and Reel  |

| NCS20164DR2G     | Quad          | No         | 20164G  | SOIC 14        | 2500 / Tape and Reel  |

| NCS20164DTBR2G** | 1             |            | TBD     | TSSOP 14       | 2500 / Tape and Reel  |

| NCV20164DR2G     | 1             | Yes        | 20164G  | SOIC 14        | 2500 / Tape and Reel  |

| NCV20164DTBR2G** | 1             |            | TBD     | TSSOP 14       | 2500 / Tape and Reel  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC Q100 Qualified and PPAP Capable.

\*\*In Development. Contact local sales office for more information.

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Rating                                                          | Symbol             | Limit                                  | Unit |

|-----------------------------------------------------------------|--------------------|----------------------------------------|------|

| Supply Voltage $(V_{DD} - V_{SS})$                              | V <sub>S</sub>     | 0.3 to 6                               | V    |

| Common Mode Input Voltage                                       | VI                 | $V_{SS} $ 0.3 to $V_{DD} \text{+} 0.3$ | V    |

| Differential Input Voltage                                      | V <sub>ID</sub>    | V <sub>DD</sub> – V <sub>SS</sub> +0.2 | V    |

| Maximum Input Current                                           | l <sub>l</sub>     | ±10                                    | mA   |

| Maximum Output Current (Note 2)                                 | Ι <sub>Ο</sub>     | ±100                                   | mA   |

| Continuous Total Power Dissipation (Note 2)                     | PD                 | 200                                    | mW   |

| Maximum Junction Temperature                                    | TJ                 | 150                                    | °C   |

| Storage Temperature Range                                       | T <sub>STG</sub>   | 65 to 150                              | °C   |

| Mounting Temperature (Infrared or Convection – 20 sec)          | T <sub>mount</sub> | 260                                    | °C   |

| ESD Capability (Note 3) Human Body Model<br>Charge Device Model | HBM<br>CDM         | 2500<br>1500                           | V    |

| Latch Up Current (Note 4)                                       | I <sub>LU</sub>    | 100                                    | mA   |

| Moisture Sensitivity Level (Note 5)                             | MSL                | Level 1                                |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS for Safe Operating Area.

Continuous short circuit operation to ground at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of the maximum output current rating over the long term may adversely affect reliability. Shorting output to either VDD or VSS will adversely affect reliability.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per JEDEC standard Js 001 2017 (AEC Q100 002) ESD Charged Device Model tested per JEDEC standard JS 002 2014 (AEC Q100 011)

ESD Charged Device Model tested per JEDEC standard JS 002 2014 (AEC Q100 011) 4. Latch up Current tested per JEDEC standard JESD78E (AEC Q100 004)

Later up current tested per JEDEC standard JESD76E (AEC G100 004

Moisture Sensitivity Level tested per IPC/JEDEC standard: J STD 020A

### OPERATING RANGES

| Parameter                                                   | Symbol          | Min                   | Max                   | Unit |

|-------------------------------------------------------------|-----------------|-----------------------|-----------------------|------|

| Operating Supply Voltage (V <sub>DD</sub> V <sub>SS</sub> ) | VS              | 1.8                   | 5.5                   | V    |

| Differential Input Voltage                                  | V <sub>ID</sub> |                       | V <sub>S</sub>        | V    |

| Common Mode Input Voltage Range                             | V <sub>CM</sub> | V <sub>SS</sub> – 0.1 | V <sub>DD</sub> + 0.1 | V    |

| Ambient Temperature                                         | T <sub>A</sub>  | 40                    | 125                   | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### THERMAL CHARACTERISTICS (Note 6)

| Package | Junction ïto ïAmbient<br>Thermal Resistance | Junction ïto ïCase Top<br>Thermal Resistance | Junction ïto ïBoard<br>Thermal Resistance | Unit |

|---------|---------------------------------------------|----------------------------------------------|-------------------------------------------|------|

|         | JA                                          | JT                                           | JB                                        |      |

.565 .90707 re f BT rf>Tj /T29fm -.00b3A>Tj /TT4 1 Tf .5808 0 TD -.0032 T7lf any of8.309 .90709 34.f B96e f 59.754 636.832 272.58 .9255BT 2 f BT 8 0 0 89

#### ELECTRICAL CHARACTERISTICS AT V $_{\rm S}$ = 1.8 V to 5.5 V

$T_A = 25^{\circ}C$ ;  $R_L$  10 k connected to mid ïsupply;  $V_{CM} = V_{OUT}$  = mid ïsupply unless otherwise noted. Boldface limits apply over the specified temperature range,  $T_A =$  ï40°C to 125°C. (Note 7)

| Parameter                                 | Symbol               | Conditions                                                                                                  | Min                                | Тур  | Max  | Unit |

|-------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------|------|------|------|

| INPUT CHARACTERISTICS                     | •                    |                                                                                                             |                                    |      |      |      |

| Input Offset Voltage                      | V <sub>OS</sub>      | $V_{S} = 5 V$                                                                                               | ï                                  | ±0.3 | ±2.1 | mV   |

|                                           |                      | V <sub>S</sub> = 5 V                                                                                        | ï                                  | ï    | ±2.6 | mV   |

| Offset Voltage Drift                      | dV <sub>OS</sub> /dT | $V_{S} = 5 V$                                                                                               | ï                                  | ±1.5 | ï    | V/°C |

| Input Bias Current (Note 7)               | I <sub>IB</sub>      |                                                                                                             | ï                                  | ±5   | ï    | pА   |

| Input Offset Current (Note 7)             | I <sub>OS</sub>      |                                                                                                             | ï                                  | ±5   | ï    | pА   |

| Channel Separation                        |                      | DC                                                                                                          | ï                                  | 100  | ï    | dB   |

| Input Capacitance                         | C <sub>IN</sub>      |                                                                                                             | ï                                  | 4    | ï    | pF   |

| Common Mode Rejection Ratio               | CMRR                 | $V_S$ = 5.5 V, $V_{CM}$ = $V_{SS}$ ï 0.1 V to $V_{DD}$ ï 1.4 V                                              | 80                                 | 103  | ï    | dB   |

|                                           |                      | $V_{S}$ = 5.5 V, $V_{CM}$ = –0.1 V to 5.6 V                                                                 | 57                                 | 79   | ï    |      |

|                                           |                      | $V_S$ = 1.8 V, $V_{CM}$ = $V_{SS}$ ï 0.1 V to $V_{DD}$ ï 1.4 V                                              | ï                                  | 91   | ï    |      |

|                                           |                      | $V_{S}$ = 1.8 V, $V_{CM}$ = –0.1 V to 1.9 V                                                                 | ï                                  | 71   | ï    |      |

| OUTPUT CHARACTERISTICS                    |                      |                                                                                                             |                                    |      |      |      |

| Open Loop Voltage Gain                    | A <sub>VOL</sub>     | $V_{S} = 1.8 \text{ V}, V_{SS} + 0.04 \text{ V} < V_{O} < V_{DD} - 0.04 \text{ V}, R_{L} = 10 \text{ k}$    | ï                                  | 100  | ï    | dB   |

|                                           |                      | $V_{S} = 5.5 \text{ V}, V_{SS} + 0.05 \text{ V} < V_{O} < V_{DD} - 0.05 \text{ V}, R_{L} = 10 \text{ k}$    | 101                                | 108  | ï    |      |

|                                           |                      | $V_{S} = 1.8 \text{ V}, V_{SS} + 0.06 \text{ V} < V_{O} < V_{DD} - 0.06 \text{ V},$<br>R <sub>L</sub> = 2 k | ï                                  | 97   | ï    |      |

|                                           |                      | $V_{S} = 5.5 \text{ V}, V_{SS} + 0.15 \text{ V} < V_{O} < V_{DD} - 0.15 \text{ V}, R_{L} = 2 \text{ k}$     | ï                                  | 113  | ï    |      |

| Short Circuit Current                     | I <sub>SC</sub>      | Output sourcing current $V_S = 5 V$                                                                         | ï                                  | 40   | ï    | mA   |

|                                           |                      | Output sinking current, $V_S = 5 V$                                                                         | ï                                  | 50   |      |      |

| Output Voltage Swing from V <sub>DD</sub> | V <sub>DD</sub> ï    | V <sub>S</sub> = 5.5 V, R <sub>L</sub> = 10 k                                                               | = 5.5 V, R <sub>L</sub> = 10 k ï 3 |      |      | mV   |

|                                           | V <sub>OH</sub>      | V <sub>S</sub> = 5.5 V, R <sub>L</sub> = 2 k                                                                | ï                                  | ï    | 60   |      |

| Output Voltage Swing from V <sub>SS</sub> | V <sub>OL</sub> ï    | i V <sub>S</sub> = 5.5 V, R <sub>L</sub> = 10 k                                                             |                                    | 3    | 20   | mV   |

|                                           | V <sub>SS</sub>      | $V_{\rm S} = 5.5 \text{ V}, \text{ R}_{\rm L} = 2 \text{ k}$                                                | ï                                  | ï    | 60   |      |

| AC CHARACTERISTICS                        |                      |                                                                                                             |                                    |      |      |      |

| Unity Gain Bandwidth                      | UGBW                 | V <sub>S</sub> = 5 V, G = +1                                                                                | ï                                  | 8    | ï    | MHz  |

| Slew Rate at Unity Gain                   | SR                   | $V_{\rm S} = 5  \rm V,  \rm G = +1$                                                                         | ï                                  | 3.5  | ï    | V/s  |

| Phase Margin                              | m                    | V <sub>S</sub> = 5 V, G = +1                                                                                | ï                                  | 52   | ï    |      |

| Gain Margin                               | A <sub>m</sub>       | -                                                                                                           | ï                                  | 11   | ï    | dB   |

| Settling Time to 0.1%                     | t <sub>S</sub>       | V <sub>S</sub> = 5 V, V <sub>IN</sub> = 2 V step, G = +1, C <sub>L</sub> = 100 pF                           | ï                                  | 0.5  | ï    | μs   |

| Settling Time to 0.01%                    | ts                   | $V_{S} = 5 V, V_{IN} = 2 V \text{ step}, G = +1, C_{L} = 100 \text{ pF}$                                    | ï                                  | 1    | ï    | μs   |

| Overload Recovery Time                    | t <sub>OR</sub>      | $V_{\rm S} = 5$ V, $V_{\rm IN}$ x gain > $V_{\rm S}$                                                        | ï                                  | 1    | ï    | μs   |

| Open Loop Output Impedance                | Z <sub>OL</sub>      | $V_{\rm S} = 5 \text{ V}, \text{ f} = 10 \text{ MHz}$                                                       | ï                                  | 240  | ï    |      |

ELECTRICAL CHARACTERISTICS AT V  $_{S}$  = 1.8 V to 5.5 V (continued) T<sub>A</sub> = 25°C; R<sub>L</sub> 10 k connected to mid supply; V<sub>CM</sub> = V<sub>OUT</sub> = mid supply unless otherwise noted. Boldface limits apply over the specified temperature range, T<sub>A</sub> = 40°C to 125°C. (Note 7)

$\label{eq:type} TYPICAL \ CHARACTERISTICS (AT \ T_A = 25^{\circ}C, \ V_{CM} = MID \ \ SUPPLY, \ C_L = 20 \ PF, \ R_L = 10 \ K \ \ TO \ MID$

## TYPICAL CHARACTERISTICS

(AT  $T_A = 25^{\circ}$

TYPICAL CHARACTERISTICS

(AT  $T_A = 25^{\circ}$ C,  $V_{CM} = MID$  SUPPLY,  $C_L = 20$  PF,  $R_L = 10$  K TO MID SUPPLY, UNLESS OTHERWISE NOTED)

$\label{eq:type} TYPICAL \ CHARACTERISTICS (AT \ T_A = 25^{\circ}C, \ V_{CM} = MID \ \ SUPPLY, \ C_L = 20 \ PF, \ R_L = 10 \ K \ \ TO \ MID$

### TYPICAL CHARACTERISTICS

(AT  $T_A = 25^{\circ}$ C,  $V_{CM} = MID$  SUPPLY,  $C_L = 20$  PF,  $R_L = 10$  K TO MID SUPPLY, UNLESS OTHERWISE NOTED)

### APPLICATION INFORMATION

The NCS20161 family of operational amplifiers is manufactured usingnsemi's CMOS process. Products in this class are general purpose, uijggin stable amplifiers and include single, dual and quad configurations.

#### Rail ïto ïRail Input with No Phase Reversal

The NCS20161 family of operational amplifiers is events (within the limits specified) trigger the protection anufactured usingnsemi's CMOS process. Products in structure so the operational amplifier is not damaged.

In order to safe guard against excessive voltages across the op amp's inputs, external clamp diodes can be used as shown in Figure 40. The four lowdrop fast diodes (Schottky preferred) are used in parallel with the internal structure to

The NCS2016x operational amplifiers are designed to divert the excessive energy to the supply rails where it can prevent phase reversal or any similar issues when the inpute easily dissipated or absorbed by the supply capacitors. pins potential exceed the supply voltages by up to 100 mV. The application designer should also take into account that

The input stage of the NCS20161 family consists of two these external diodes add leakage currents and parasitic differential CMOS input stages connected in parallel: the first is constructed using paired PMOS devices and it operates at low common mode input voltages ( $\chi$ ) the secondstage is build using paired NMOS devices to operate Limiting Input Currents at high V<sub>CM</sub>. The transition between the two input stages occurs at a common mode input voltage of approximately V<sub>DD</sub> ï1.3V.

#### Limiting Input Voltages

In order to prevent damage and/or improper operation of these amplifiers, the application circuit must never expose the input pins to voltages or currents higher than the Absolute Maximum Ratings.

The internal ESD structure includes special diodes to protect the input stages while maintaining a low input bias current ( $I_B$ ). The input protection circuitry clamp the inputs when the signals applied exceed more than one diode drop below VSS or one diode drop above VDD. Very fast ESD

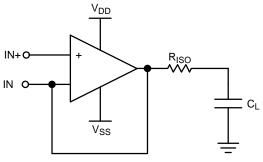

Figure 41. Driving Capacitive Loads

Simulating the application with semi's Spice model is a good starting point for selecting the isolation resistor's value.Bench testing the frequency and step response can be used to fineitune the value according to the desired characteristic.

#### Unity Gain Bandwidth

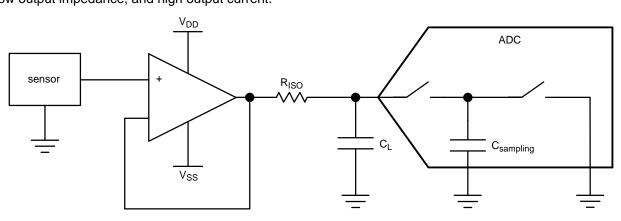

Interfacing a high impedance sensor's output to will match the input. The differential input voltage is limited a relatively lowiimpedance ADC input usually requires an only by the ESD protection structure and not by intermediatestage to avoid unwanted interference of the two backito ibackdiodes between inputs. devices, and this stage needs to have a high input impedance,

a low output impedance, and high output current.

The unity gain buffer is recommended here (Figure 42). The ADC's internal sampling capacitor requires a buffer front ïend torecharge it faster than the sampling time, and this problem is even worse if more channels are sampled by the same ADC using an internal multiplexer. In order to achieve a settling time shorter than the multiplexed sampling rate, an RC stage is recommended between the buffer and the ADC input. The So resistor's value should be low enough to charge the capacitor quickly, but at the same time large enough to isolate the capacitive load from the amplifier output to preserve phase margin. When transients argenerated by the sensor's output, first the two amplifier inputs see a high differential voltage between them, then the output settles and brings the inverting input back to the correct voltage.

Let us take an example of a 0.1 V to 4 V sensor signal. To successfully accommodate it, the differential input range of the NCS2016x is close to the supply range and the output

Figure 42. Unity Gain Buffer Stage for Sampling with ADC

#### Power Supply Bypassing

crosstalkincreased current consumption, or add noise to the For AC, the power supply pins (VDD and VSS for split supply rails.

supply, VDD for single supply) should be bypassed locally with a quality capacitor in the range of 100 nF as close as possible to the amplifier supply pins. Ceramic capacitors are recommended for their low ESR and good high frequency response.

For DC, a bulk capacitor in the range of A placed within inches distance from the appropriate provide the additional current needed to drive higher loads.

#### **Unused Operational Amplifiers**

Occasionally not all the op amp channels offered in the quad packages are needed for a specific application. They can be connected as "buffering ground" as shown in Figure 43, a solution that does not need any extra parts. Connecting them differently (inputs split to rails, left floating, etc.) can sometimes cause unwanted oscillation,

Figure 43. Unused Operational Amplifiers

PACKAGE DIMENSIONS

### PACKAGE DIMENSIONS

TSOP ï5 3.00x1.50x0.95, 0.95P CASE 483 ISSUE P

A٢

### PACKAGE DIMENSIONS

Micro8 CASE 846A 02 ISSUE K NDTES: MILLIMETER DIM MIN. NDM. Α \_ A1 0.05 0.08 0.13 0.18 с Е RECOMMENDED MOUNTING FOOTPRINT