# Fixed Current-Limiting Power-Distribution Switches

# **NCP382**

The NCP382 is a single input dual outputs high side power–distribution switch designed for applications where heavy capacitive loads and short–circuits are likely to be encountered. The device includes an integrated 80 m $\Omega$ , P–channel MOSFET. The device limits the output current to a desired level by switching into a constant–current mode when the output load exceeds the current–limit threshold or a short is present. The current–limit threshold is internally fixed. The power–switches rise and fall times are controlled to minimize current ringing during switching.

The FLAG logic output asserts low during overcurrent or overtemperature conditions. The switch is controlled by a logic enable input active high or low.

#### **Features**

- 2.5 V 5.5 V Operating Range

- 80 mΩ High–Side MOSFET

- Current Limit: Fixed 500 mA, 1 A and 1.5 A

- Undervoltage Lock–Out (UVLO)

- Soft-Start Prevents Inrush Current

- Thermal Protection

- Soft Turn-Off

- Enable Active High or Low (EN or EN)

- Compliance to IEC61000-4-2 (Level 4)

- 8.0 kV (Contact)

- ◆ 15 kV (Air)

- UL Listed for SOIC package (NCP382xDxxxx) File No. E343275

- IEC60950 -

dimensions section on page 10 of this data sheet.

XXXXX = Specific Device Code A = Assembly Location

L = Wafer Lot Y = Year

W = Work Week

■ Pb-Free Package

### **ORDERING INFORMATION**

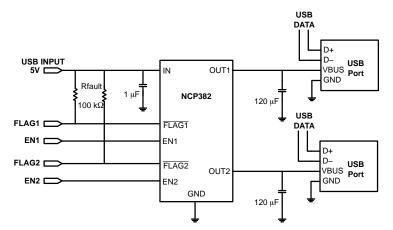

Figure 1. Typical Application Circuit

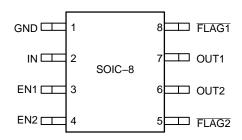

Figure 2. Pin Connections

# PIN FUNCTION DESCRIPTION

| Pin Name | Type | Description                                                                                                                                                                                                                        |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN1      | - 1  | Enable 1 input, logic low/high (i.e. $\overline{\text{EN}}$ or $\overline{\text{EN}}$ ) turns on power switch.                                                                                                                     |

| EN2      | I    | Enable 2 input, logic low/high (i.e. EN or EN) turns on power switch.                                                                                                                                                              |

| GND      | Р    | Ground connection.                                                                                                                                                                                                                 |

| IN       | Р    | Power–switch input voltage; connect a 1 $\mu$ F or greater ceramic capacitor from IN to GND as close as possible to the IC.                                                                                                        |

| FLAG1    | 0    | Active–low open–drain output 1, asserted during overcurrent or overtemperature conditions. Connect a 10 k $\Omega$ or greater resistor pull–up, otherwise leave unconnected.                                                       |

| FLAG2    | 0    | Active–low open–drain output 2, asserted during overcurrent or overtemperature conditions. Connect a 10 k $\Omega$ or greater resistor pull–up, otherwise leave unconnected.                                                       |

| OUT1     | 0    | Power–switch output1; connect a 1 $\mu$ F ceramic capacitor from OUT1 to GND, as close as possible to the IC. This minimum value is recommended for USB requirement in terms of load transient response and strong short circuits. |

| OUT2     | 0    | Power–switch output2; connect a 1 $\mu$ F ceramic capacitor from OUT2 to GND, as close as possible to the IC. This minimum value is recommended for USB requirement in terms of load transient response and strong short circuits. |

# **MAXIMUM RATINGS**

| Rating                                                   | Symbol                                                                                                                             | Value        | Unit |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------|------|

| From IN to OUT1, From IN to OUT2 Supply Voltage (Note 1) | $V_{IN}$ , $V_{OUT1}$ , $V_{OUT2}$                                                                                                 | -7.0 to +7.0 | V    |

| IN, OUT1,OUT2, EN1, EN2, FLAG1, FLAG2 (Note 1)           | V <sub>IN,</sub> V <sub>OUT1,</sub> V <sub>OUT2,</sub> V <sub>EN1,</sub> V <sub>EN2,</sub> V <sub>FLAG1</sub> , V <sub>FLAG2</sub> | -0.3 to +7.0 | V    |

| FLAG1, FLAG2 sink current                                | I <sub>SINK</sub>                                                                                                                  | 1.0          | mA   |

ESD Withstand Voltage (IEC 61000–4–2) (output only, when bypassed with 1.0  $\mu\text{F}$  capacitor minimum)

**ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-40^{\circ}C$  to  $+85^{\circ}C$  and  $T_J$  up to + 125°C for  $V_{IN}$  between 2.5 V to 5.5 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 5$  V.

| Symbol              | Parameter                               | Conditions                                            | Min | Тур | Max | Unit |

|---------------------|-----------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| POWER S             | SWITCH                                  |                                                       |     |     |     |      |

| R <sub>DS(on)</sub> | Static drain-source on-state resistance | $T_J = 25^{\circ}C$ , $V_{IN} = 3.6 \text{ V to 5 V}$ |     | 80  | 110 | mΩ   |

|                     |                                         | V <sub>IN</sub> = 5 V −40°                            |     |     |     |      |

| IN | OUT1  |

|----|-------|

| N  | CP382 |

|    |       |

|    |       |

|    | GND   |

\_

### **Enable Input**

Enable pin must be driven by a logic signal (CMOS or TTL compatible) or connected to the GND or VIN. A logic low on  $\overline{ENX}$  or high on ENX turns—on the device. A logic high on  $\overline{ENX}$  or low on ENX turns off device and reduces the current consumption down to  $I_{INOFF}$ .

### **Blocking Control**

The blocking control circuitry switches the bulk of the power MOS. When the part is off, the body diode limits the

leakage current I<sub>REV</sub> from OUTX to IN. In this mode, anode of the body diode is connected to IN pin and cathode is connected to OUTX pin. In operating condition, anode of the body diode is connected to OUTX pin and cathode is connected to IN pin preventing the discharge of the power supply.

### **APPLICATION INFORMATION**

#### **Power Dissipation**

The junction temperature of the device depends on different contributing factors such as board layout, ambient temperature, device environment, etc... Yet, the main contributor in term of junction temperature is the power dissipation of the power MOSFET. Assuming this, the power dissipation and the junction temperature in normal mode can be calculated with the following equations:

$$P_D = R_{DS(on)} \times \left( \left( I_{OUT1} \right)^2 + \left( I_{OUT2} \right)^2 \right)$$

(eq. 2)

$P_{D}$

### **ORDERING INFORMATION**

| Device               | Marking | Active<br>Enable<br>Level | Over<br>Current<br>Limit | Evaluation<br>Board  | UL<br>236<br>7 | IEC60950<br>Ed2 (CB<br>Scheme) | IEC60950<br>Ed2 Ad1,<br>Ad2 | Package             | Shipping <sup>†</sup> |

|----------------------|---------|---------------------------|--------------------------|----------------------|----------------|--------------------------------|-----------------------------|---------------------|-----------------------|

| NCP382LD05AA-<br>R2G | 382L05  |                           | 0.5 A                    | NCP382LD<br>05AAGEVB | Y              | Y                              | Y                           |                     | •                     |

|                      | •       | ENx<br>Low                | •                        | •                    | •              | •                              | •                           |                     |                       |

|                      |         |                           |                          |                      |                |                                |                             | SOIC-8<br>(Pb-Free) | 2500 /                |

|                      |         |                           |                          |                      |                |                                |                             |                     |                       |

|                      |         |                           |                          |                      |                |                                |                             |                     |                       |

| С | 1.35 | 1.75 | 0.053          | 0.069    |       |       |

|---|------|------|----------------|----------|-------|-------|

| D | 0.33 | 0.51 | <b>CC1.3</b> 5 | 0.02.075 | 0.053 | 0.069 |

| G |      |      |                |          |       |       |