# 1.3 Watt Audio Power Amplifier with Fast Turn On Time

| The NCP2892 396 us0 T00e1eTD-0.0008 NCP28,CP2892 O 0 0 T2 | Semico2-0.3 Wc]TJ3(o)0 T3(m)0 | T3(m)0 T3(uni)-ept(c]TJ3 |

|-----------------------------------------------------------|-------------------------------|--------------------------|

| low-power consumption shutdown mode, which is achieved by |                               |                          |

| driving the SHUTDOWN                                      |                               |                          |

pin with logic low.

The NCP2892 contains circuitry to prevent from "pop and click" noise that would otherwise occur during turn-on and turn-off transitions.

For maximum flexibility, the NCP2892 provides an externally controlled gain (with resistors), as well as an externally controlled turn—on time (with the bypass capacitor). When using a 1  $\mu$ F bypass capacitor, it offers 100 ms wake up time.

Due to its excellent PSRR, it can be directly connected to the battery, saving the use of an LDO.

This device is available in a 9-Pin Flip-Chip CSP (Lead-Free).

#### **Features**

- 1.3 W to an 8.0  $\Omega$  BTL Load from a 5.0 V Power Supply

- Excellent PSRR: Direct Connection to the Battery

- "Pop and Click" Noise Protection Circuit

- Ultra Low Current Shutdown Mode: 10 nA

- 2.2 V-5.5 V Operation

- External Gain Configuration Capability

- External Turn-on Time Configuration Capability: 100 ms (1 μF Bypass Capacitor)

- Up to 1.0 nF Capacitive Load Driving Capability

- Thermal Overload Protection Circuitry

- This is a Pb-Free Device\*

#### **Typical Applications**

- Portable Electronic Devices

- PDAs

- Wireless Phones

9-Pin Flip-Chip CSP FC SUFFIX CASE 499E

MAx = Specific Device Code

#### **PIN CONNECTIONS**

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Ŧ

Figure 1. Typical

### **PIN DESCRIPTION**

Pin Type Symbol Description

# $\textbf{ELECTRICAL CHARACTERISTICS} \ \text{Limits apply for } T_{\underline{A}} \ \text{between } -40^{\circ}\text{C to } +85^{\circ}\text{C (Unless otherwise noted)}.$

| Characteristic           | Symbol            | Conditions                                                         | Min<br>(Note 7) | Тур               | Max<br>(Note 7) | Unit |

|--------------------------|-------------------|--------------------------------------------------------------------|-----------------|-------------------|-----------------|------|

| Supply Quiescent Current | I <sub>dd</sub>   | $V_p = 2.6 \text{ V}$ , No Load $V_p = 5.0 \text{ V}$ , No Load    | _<br>_          | 1.5<br>1.7        | 4               | mA   |

|                          |                   | $V_p = 2.6 \text{ V}, 8 \Omega$<br>$V_p = 5.0 \text{ V}, 8 \Omega$ | _<br>_          | 1.7<br>1.9        | 5.5             |      |

| Common Mode Voltage      | V <sub>cm</sub>   | -                                                                  | -               | V <sub>p</sub> /2 | -               | V    |

| Shutdown Current         | I <sub>SD</sub>   | $T_A = +25^{\circ}C$<br>$T_A = -40^{\circ}C$ to +85°C              | -               | 0.01              | 0.5<br>1.0      | μΑ   |

| Shutdown Voltage High    | V <sub>SDIH</sub> | -                                                                  | 1.2             | _                 | _               | V    |

| Shutdown Voltage Low     | V <sub>SDIL</sub> | -                                                                  | -               | -                 | 0.4             | V    |

| Turning On Time (Note 9) | T <sub>WU</sub>   | $C_{by} = 1 \mu FC$                                                | •               | •                 | •               | •    |

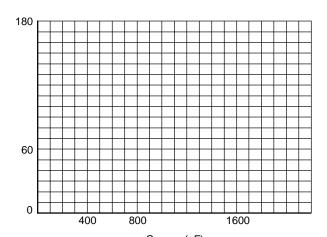

$C_{bypass} \, (nF)$  Figure 21.  $T_{ON}$  versus  $C_{bypass} \, @ V_{bat} = 3.6 \text{ V},$   $T_{A} = +25^{\circ}\text{C}$

Figure 22.  $T_{ON}$  versus Temperature @  $V_{bat}$  = 3.6 V,  $C_{bypass}$  = 1  $\mu F$

Figure 23.

$$T_{ON}$$

vs.  $V_{bat}$  @  $C_{bypass}$  = 1  $\mu$ F,  $T_A$  = +25°C

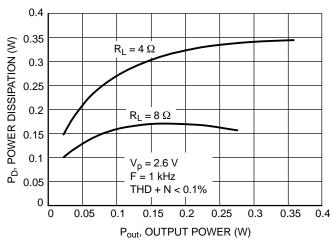

Figure 24. Power Dissipation versus Output Power

Figure 25. Power Dissipation versus Output Power

Figure 26. Power Dissipation versus Output Power

700 PCB Heatsink Area  $200 \, \text{mm}^2$ 500 mm<sup>2</sup> 50 mm<sup>2</sup>  $P_{Dmax} = 633 \text{ mW}$ for  $V_p = 5 V$ ,  $R_L = 8 \Omega$ 0 0 20 40 60 80 100 120 140 160 T<sub>A</sub>, AMBIENT TEMPERATURE (°C)

Figure 27. Power Dissipation versus Output Power

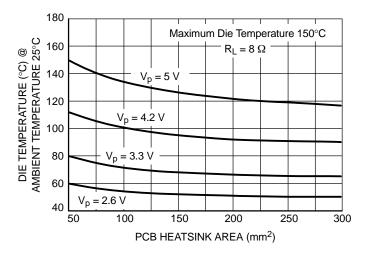

Figure 28. Power Derating - 9-Pin Flip-Chip CSP

Figure 29. Maximum Die Temperature versus PCB Heatsink Area

#### APPLICATION INFORMATION

#### **Detailed Description**

The NCP2892 audio amplifier can operate under 2.6 V until 5.5 V power supply. With less than 1% THD+N, B version can deliver up to 1.2 W rms output power to an 8.0  $\Omega$  load (V<sub>p</sub> = 5.0 V). If application allows to reach 10% THD+N, then 1.6 W can be provided using a 5.0 V power supply.

The structure of the NCP2892 is basically composed of two identical internal power amplifiers; the first one is externally configurable with gain–setting resistors  $R_{in}$  and  $R_f$  (the closed–loop gain is fixed by the ratios of these resistors) and the second is internally fixed in an inverting unity–gain configuration by two resistors of 20 k $\Omega$ . So the load is driven differentially through OUTA and OUTB outputs. This configuration eliminates the need for an output coupling capacitor. The NCP2892A has around 100  $\Omega$  and the NCP2892B has around 10 k $\Omega$  output impedance in the shutdown mode.

#### **Internal Power Amplifier**

The output PMOS and NMOS transistors of the amplifier were designed to deliver the output power of the specifications without clipping. The channel resistance ( $R_{on}$ ) of the NMOS and PMOS transistors does not exceed 0.6  $\Omega$  when they drive current.

The structure of the internal power amplifier is composed of three symmetrical gain stages, first and medium gain stages are transconductance gain stages to obtain maximum bandwidth and DC gain.

#### Turn-On and Turn-Off Transitions

A cycle with a turn-on and turn-off transition is illustrated with plots that show both single ended signals on the previous page.

In order to eliminate "pop and click" noises during transitions, output power in the load must be slowly established or cut. When logic high is applied to the shutdown pin, the bypass voltage begins to rise exponentially and once the output DC level is around the common mode voltage, the gain is established instantaneously. This way to turn—on the device is optimized in terms of rejection of "pop and click" noises.

The device has the same behavior when it is turned-off by a logic low on the shutdown pin. During the shutdown mode, amplifier outputs are connected to the ground.

When a shutdown low level is applied, with 1  $\mu$ F bypass capacitor, it takes 65 ms before the DC output level is tied to Ground on each output. However, no audio signal will be provided to the BTL load only 1  $\mu$ s after the falling edge on the shutdown pin.

With 1  $\mu$ F bypass capacitor, turn on time is set to 90 ms. This fast turn on time added to a very low shutdown current saves battery life and brings flexibility when designing the audio section of the final application.

NCP2892 is a zero pop noise device when using a differential audio input. In case of a single ended one, there

is no audible pop click noise, especially when the input cut off frequency is higher than 100 Hz.

#### **Shutdown Function**

The device enters shutdown mode when shutdown signal is low. During the shutdown mode, the DC quiescent current of the circuit does not exceed 100 nA. In this configuration, the output impedance is 10 k $\Omega$  on each output.

#### **Current Limit Circuit**

The maximum output power of the circuit (Porms = 1.0 W,  $V_p = 5.0 \text{ V}$ ,  $R_L = 8.0 \Omega$ ) requires a peak current in the load of 500 mA.

In order to limit the excessive power dissipation in the load when a short-circuit occurs, the current limit in the load is fixed to 800 mA. The current in the four output MOS transistors are real-time controlled, and when one current exceeds 800 mA, the gate voltage of the MOS transistor is clipped and no more current can be delivered.

#### **Thermal Overload Protection**

Internal amplifiers are switched off when the temperature exceeds 160°C, and will be switched on again only when the temperature decreases fewer than 140°C.

The NCP2892 is unity-gain stable and requires no external components besides gain-setting resistors, an input coupling capacitor and a proper bypassing capacitor in the typical application.

The first amplifier is externally configurable ( $R_f$  and  $R_{in}$ ), while the second is fixed in an inverting unity gain configuration.

The differential-ended amplifier presents two major advantages:

- The possible output power is four times larger (the output swing is doubled) as compared to a single-ended amplifier under the same conditions.

- Output pins (OUTA and OUTB) are biased at the same potential  $V_p/2$ , this eliminates the need for an output coupling capacitor required with a single-ended amplifier configuration.

The differential closed loop-gain of the amplifier is

given by

$$A_{Vd}$$

= 2 \*  $\frac{R_f}{R_{in}} = \frac{V_{orms}}{V_{inrms}}$ .

Output power delivered to the load is given by

$$P_{orms} = \frac{(Vopeak)^2}{2 R_L}$$

(Vopeak is the peak differential output voltage).

When choosing gain configuration to obtain the desired output power, check that the amplifier is not current limited or clipped.

The maximum current which can be delivered to the load

is 500 mA

$$l_{opeak} = \frac{V_{opeak}}{R_L}$$

.

| Gain-Setting |  |  |

|--------------|--|--|

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

Silkscreen Layer

Figure 35. Demonstration Board for 9-Pin Flip-Chip CSP Device - PCB Layers

#### **BILL OF MATERIAL**

| Item | Part Description                    | Ref.   | PCB<br>Footprint | Manufacturer     | Manufacturer<br>Reference |

|------|-------------------------------------|--------|------------------|------------------|---------------------------|

| 1    | NCP2892 Audio Amplifier             | -      | -                | ON Semiconductor | NCP2892                   |

| 2    | SMD Resistor 20 K $\Omega$          | R1, R5 | 0805             | Panasonic        | ERJ-6GEYJ203V             |

| 3    | SMD Resistor 100 K $\Omega$         | R2, R4 | 0805             | Panasonic        | ERJ-6GEYJ104V             |

| 4    | SMD Resistor 150 KΩ                 | R3     | 0805             | Panasonic        | ERJ-6GEYJ154V             |

| 5    | Ceramic Capacitor 100 nF, 100 V X7R | C1, C5 | 0805             | TDK              | C2012X7R2A473K            |

DATE 30 JUN 2004

SCALE 4:1

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 0.540       | 0.660 |  |

| A1  | 0.210       | 0.270 |  |

| A2  |             |       |  |