# 2.65 W Filterless Class-D Audio Power Amplifier

The NCP2820 is a cost effective mono Class D audio power amplifier capable of delivering 2.65 W of continuous average power to 4.0 from a 5.0 V supply in a Bridge Tied Load (BTL) configuration. Under the same conditions, the output power stage can provide 1.4 W to a 8.0 BTL load with less than 1% THD+N. For cellular handsets or PDAs it offers space and cost savings because no output filter is required when using inductive tranducers. With more than 90% efficiency and very low shutdown current, it increases the lifetime of your battery and drastically lowers the junction temperature.

The NCP2820 processes analog inputs with a pulse width modulation technique that lowers output noise and THD when compared to a conventional sigma delta modulator. The device allows independent gain while summing signals from various audio sources. Thus, in cellular handsets, the earpiece, the loudspeaker and even the melody ringer can be driven with a single NCP2820. Due to its low 42, V noise floor, A weighted, a clean listening is guaranteed no matter the load sensitivity. With zero pop and click noise performance NCP2820A turns on within 1 ms versus 9 ms for NCP2820 version.

#### Features

- Optimized PWM Output Stage: Filterless Capability

- Efficiency up to 90%

- Low 2.5 mA Typical Quiescent Current

- $\bullet\,$  Large Output Power Capability: 1.4 W with 8.0  $\,$  Load (CSP) and THD + N < 1%  $\,$

- Ultra Fast Start up Time: 1 ms for NCP2820A Version

- High Performance, THD+N of 0.03% @  $V_p = 5.0$  V,  $R_L = 8.0$  ,  $P_{out} = 100$  mW

- Excellent PSRR ( 65 dB): No Need for Voltage Regulation

- Surface Mounted Package 9 Pin Flip Chip CSPand UDFN8

- Fully Differential Design. Eliminates Two Input Coupling Capacitors

- Very Fast Turn On/Off Times with Advanced Rising and Falling Gain Technique

- External Gain Configuration Capability

- Internally Generated 250 kHz Switching Frequency

- "Pop and Click" Noise Protection Circuitry

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC Q100 Qualified and PPAP Capable

- These are Pb Free Devices

#### Applications

- Cellular Phone

- Portable Electronic Devices

- PDAs and Smart Phones

- Portable Computer

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 19 of this data sheet.

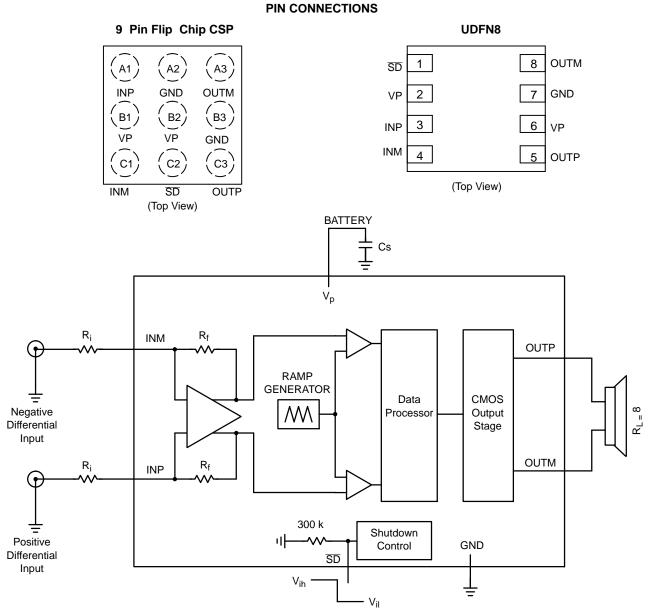

#### PIN DESCRIPTION

| Pin | Pin No. |        |      |                                                                                                                                                                                                                                    |  |  |  |

|-----|---------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CSP | UDFN8   | Symbol | Туре | Description                                                                                                                                                                                                                        |  |  |  |

| A1  | 3       | INP    | I    | Positive Differential Input.                                                                                                                                                                                                       |  |  |  |

| A2  | 7       | GND    | I    | Analog Ground.                                                                                                                                                                                                                     |  |  |  |

| A3  | 8       | OUTM   | 0    | Negative BTL Output.                                                                                                                                                                                                               |  |  |  |

| B1  | 2       | Vp     | I    | Analog Positive Supply. Range: 2.5 V – 5.5 V.                                                                                                                                                                                      |  |  |  |

| B2  | 6       | Vp     | I    | Power Analog Positive Supply. Range: 2.5 V – 5.5 V.                                                                                                                                                                                |  |  |  |

| B3  | 7       | GND    | I    | Analog Ground.                                                                                                                                                                                                                     |  |  |  |

| C1  | 4       | INM    | I    | Negative Differential Input.                                                                                                                                                                                                       |  |  |  |

| C2  | 1       | SD     | I    | The device enters in Shutdown Mode when a low level is applied on this pin. An internal $300 \text{ k}$ resistor will force the device in shutdown mode if no signal is applied to this pin. It also helps to save space and cost. |  |  |  |

| C3  | 5       | OUTP   | 0    | Positive BTL Output.                                                                                                                                                                                                               |  |  |  |

#### MAXIMUM RATINGS

| Symbol           | Rating                                                                           |                              | Max                          | Unit<br>V |  |

|------------------|----------------------------------------------------------------------------------|------------------------------|------------------------------|-----------|--|

| Vp               | Supply Voltage                                                                   | Active Mode<br>Shutdown Mode | 6.0<br>7.0                   |           |  |

| V <sub>in</sub>  | Input Voltage                                                                    |                              | –0.3 to V <sub>CC</sub> +0.3 | V         |  |

| l <sub>out</sub> | Max Output Current (Note 1)                                                      |                              | 1.5                          | А         |  |

| Pd               | Power Dissipation (Note 2)                                                       |                              | Internally Limited           | -         |  |

| T <sub>A</sub>   | Operating Ambient Temperature                                                    |                              | -40 to +85                   | °C        |  |

| TJ               | Max Junction Temperature                                                         |                              | 150                          | °C        |  |

| T <sub>stg</sub> | Storage Temperature Range                                                        |                              | -65 to +150                  | °C        |  |

| R <sub>JA</sub>  | Thermal Resistance Junction-to-Air                                               | 9–Pin Flip–Chip<br>UDFN8     | 90 (Note 3)<br>50            | °C/W      |  |

|                  | ESD Protection<br>Human Body Model (HBM) (Note 4)<br>Machine Model (MM) (Note 5) |                              | > 2000<br>> 200              | V         |  |

| -                | Latchup Current @ $T_A = 85^{\circ}C$ (Note 6)                                   | 9–Pin Flip–Chip<br>UDFN8     | ±70<br>±100                  | mA        |  |

| MSL              | Moisture Sensitivity (Note 7)                                                    |                              | Level 1                      |           |  |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. The device is protected by a current breaker structure. See "Current Breaker Circuit" in the Description Information section for more information.

The thermal shutdown is set to 160°C (typical) avoiding irreversible damage to the device due to power dissipation.

For the 9–Pin Flip–Chip CSP package, the R JA is highly dependent of the PCB Heatsink area. For example, R JA can equal 195°C/W with 50 mm<sup>2</sup> total area and also 135°C/W with 500 mm<sup>2</sup>. When using ground and power planes, the value is around 90°C/W, as specified in table.

4. Human Body Model: 100 pF discharged through a 1.5 k resider following specification JESD22/A114. On 9-Pin Flip-Chip, B2 Pin (VP) is qualified at 1500 V. Machine Model: 200 pF discharged through all pins following specification JESD22/A115.

Latchup Testing per JEDEC Standard JESD78.

7. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

| Characteristic           | Symbol          | Conditions                                                                                                                                                                                               | Min | Тур | Max | Unit |

|--------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Operating Supply Voltage | Vp              | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                                                                                                                                                   | 2.5 | -   | 5.5 | V    |

| Supply Quiescent Current | I <sub>dd</sub> | $V_p = 3.6 \text{ V}, \text{ R}_L = 8.0$ $V_p = 5.5 \text{ V}, \text{ No Load}$ $V_p \text{ from } 2.5 \text{ V to } 5.5 \text{ V}, \text{ No Load}$ $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | -   |     |     |      |

ELECTRICAL CHARACTERISTICS (Limits apply for T

| Characteristic                    | Symbol | Conditions                                                                                                                                                                                                                                              | Min              | Тур                                  | Max | Unit |

|-----------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|-----|------|

| RMS Output Power                  | Po     | $\begin{array}{c} {\sf R}_L = 8.0  ,  f = 1.0 \; {\sf kHz},  {\sf THD}{\sf +N} < 1\% \\ {\sf V}_p = 2.5 \; {\sf V} \\ {\sf V}_p = 3.0 \; {\sf V} \\ {\sf V}_p = 3.6 \; {\sf V} \\ {\sf V}_p = 4.2 \; {\sf V} \\ {\sf V}_p = 5.0 \; {\sf V} \end{array}$ | -<br>-<br>-<br>- | 0.22<br>0.33<br>0.45<br>0.67<br>0.92 |     | W    |

|                                   |        | $\begin{array}{c} {\sf R}_L = 8.0  , \ f = 1.0 \ {\sf kHz}, \ {\sf THD}{+}{\sf N} < 10\% \\ {\sf V}_p = 2.5 \ {\sf V} \\ {\sf V}_p = 3.0 \ {\sf V} \\ {\sf V}_p = 3.6 \ {\sf V} \\ {\sf V}_p = 4.2 \ {\sf V} \\ {\sf V}_p = 5.0 \ {\sf V} \end{array}$  | -<br>-<br>-<br>- | 0.36<br>0.53<br>0.76<br>1.07<br>1.49 |     | W    |

|                                   |        | $\begin{array}{c} {\sf R}_{\sf L}=4.0  ,  f=1.0 \; {\sf kHz},  {\sf THD}{\sf +N}<1\% \\ {\sf V}_p=2.5 \; {\sf V} \\ {\sf V}_p=3.0 \; {\sf V} \\ {\sf V}_p=3.6 \; {\sf V} \\ {\sf V}_p=4.2 \; {\sf V} \\ {\sf V}_p=5.0 \; {\sf V} \end{array}$           | -<br>-<br>-<br>- | 0.24<br>0.38<br>0.57<br>0.83<br>1.2  |     | W    |

|                                   |        | $ \begin{array}{c} {\sf R}_L = 4.0  , \ f = 1.0 \ {\sf kHz}, \ {\sf THD}{\sf +N} < 10\% \\ {\sf V}_p = 2.5 \ {\sf V} \\ {\sf V}_p = 3.0 \ {\sf V} \\ {\sf V}_p = 3.6 \ {\sf V} \\ {\sf V}_p = 4.2 \ {\sf V} \\ {\sf V}_p = 5.0 \ {\sf V} \end{array} $  | -<br>-<br>-<br>- | 0.52<br>0.8<br>1.125<br>1.58<br>2.19 |     | W    |

| Efficiency                        | -      | $\begin{array}{l} {\sf R}_{\sf L} = 8.0  , {\sf f} = 1.0 \; {\sf kHz} \\ {\sf V}_{\sf p} = 5.0 \; {\sf V}, \; {\sf P}_{out} = 1.2 \; {\sf W} \\ {\sf V}_{\sf p} = 3.6 \; {\sf V}, \; {\sf P}_{out} = 0.6 \; {\sf W} \end{array}$                        |                  | 87<br>87                             | -   | %    |

|                                   |        | $\begin{array}{l} {\sf R}_{\sf L} = 4.0  ,  {\sf f} = 1.0 \; {\sf KHz} \\ {\sf V}_{\sf p} = 5.0 \; {\sf V}, \; {\sf P}_{out} = 2.0 \; {\sf W} \\ {\sf V}_{\sf p} = 3.6 \; {\sf V}, \; {\sf P}_{out} = 1.0 \; {\sf W} \end{array}$                       | _<br>_           | 79<br>78                             | -   |      |

| Total Harmonic Distortion + Noise | THD+N  | $\begin{split} V_p &= 5.0 \text{ V}, \text{ R}_L = 8.0  , \\ f &= 1.0 \text{ kHz}, \text{ P}_{out} = 0.25 \text{ W} \\ V_p &= 3.6 \text{ V}, \text{ R}_L = 8.0  , \end{split}$                                                                          | -                | 0.05                                 | -   | %    |

| Common Mode Rejection Ratio       | CMRR   | $f = 1.0 \text{ kHz}, P_{out} = 0.25 \text{ W}$ $V_{p} \text{ from } 2.5 \text{ V to } 5.5 \text{ V}$ $V_{ic} = 0.5 \text{ V to } V_{p} - 0.8 \text{ V}$ $V_{ic} = 2.6 \text{ V V} = 4.0 \text{ V}$                                                     | -                | 0.06<br>-62                          | -   | dB   |

|                                   |        | $V_p = 3.6 V, V_{ic} = 1.0 V_{pp}$<br>f = 217 Hz<br>f = 1.0 kHz                                                                                                                                                                                         | -                | -56<br>-57                           | -   |      |

| Power Supply Rejection Ratio      | PSRR   | $\label{eq:Vp_ripple_pk-pk} \begin{array}{l} V_{p\_ripple\_pk-pk} = 200 \mbox{ mV}, \ R_L = 8.0 \ , \\ \mbox{Inputs AC Grounded} \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                               |                  | -62<br>-65                           | -   | dB   |

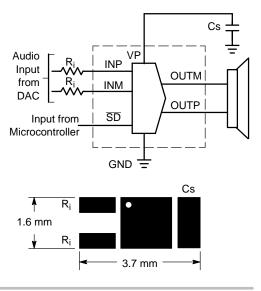

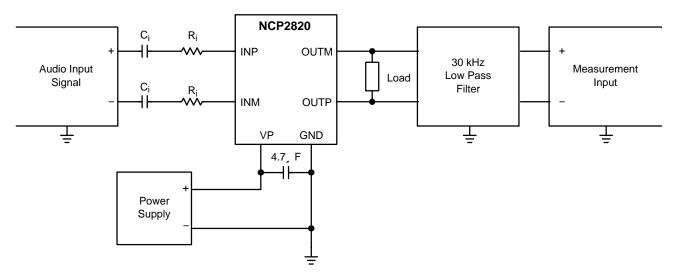

Figure 2. Test Setup for Graphs

NOTES:

1. Unless otherwise noted,  $C_i = 100 \ \text{nF}$  and  $R_i \text{=} 150 \ \text{k}$

### **TYPICAL CHARACTERISTICS**

| <br> |  |  | <br> | <br> |

|------|--|--|------|------|

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

|      |  |  |      |      |

| <br> | <br> | <br> |  |

|------|------|------|--|

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

EFFICIENCY %

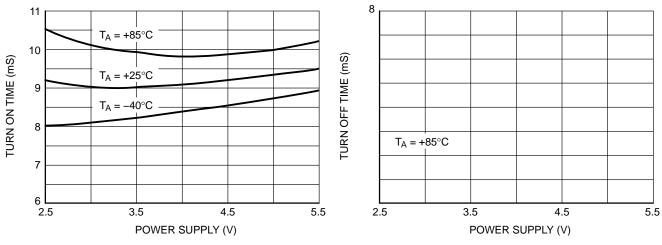

Figure 33. Turn on Time

Figure 34. Turn off Time

### **APPLICATION INFORMATION**

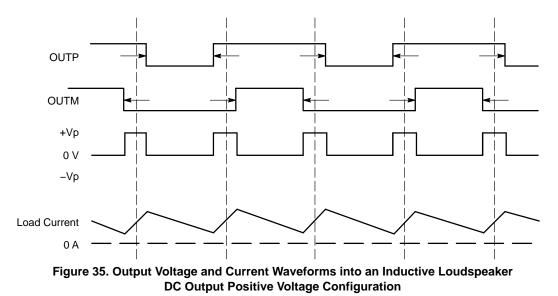

#### NCP2820 PWM Modulation Scheme

The NCP2820 uses a PWM modulation scheme with each output switching from 0 to the supply voltage. If  $V_{in} = 0 V$  outputs OUTM and OUTP are in phase and no current is flowing through the differential load. When a positive signal

is applied, OUTP duty cycle is greater than 50% and OUTM is less than 50%. With this configuration, the current through the load is 0 A most of the switching period and thus power losses in the load are lowered.

#### Voltage Gain

The first stage is an analog amplifier. The second stage is

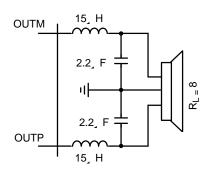

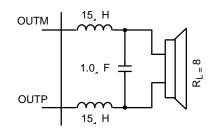

Figure 37. Optional Audio Output Filter

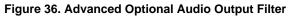

Figure 38. Optional EMI Ferrite Bead Filter

Figure 41. NCP2820 Application Schematic with Differential Input Configuration and High Pass Filtering Function

NCP2820 Series

Figure 45. Silkscreen Layer of the UDFN8 Evaluation Board

#### **PCB Layout Information**

NCP2820 is suitable for low cost solution. In a very small package it gives all the advantages of a Class D audio amplifier. The required application board is focused on low cost solution too. Due to its fully differential capability, the audio signal can only be provided by an input resistor. If a low pass filtering function is required, then an input coupling capacitor is needed. The values of these components determine the voltage gain and the bandwidth frequency. The battery positive supply voltage requires a good decoupling capacitor versus the expected distortion.

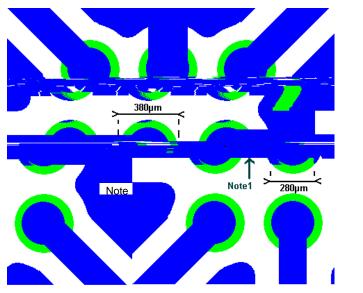

#### Figure 46. Top Layer of Two Layers Board Dedicated to the 9 Pin Flip Chip Package

Note: This track between Vp pins is only needed when a 2 layers board is used. In case of a typical 4 or more layers, the use of laser vias in pad will optimize the THD+N floor. The demonstration board delivered by ON Semiconductor is a 4 Layers with Top, Ground, Power Supply and Bottom.

#### **Bill of Materials**

| Item | Part Description                    | Ref    | PCB<br>Footprint | Manufacturer    | Part Number     |

|------|-------------------------------------|--------|------------------|-----------------|-----------------|

| 1    | NCP2820 Audio Amplifier             | U1     |                  |                 | NCP2820         |

| 2    | SMD Resistor 150 k                  | R1, R2 | 0603             | Vishay-Draloric | CRCW0603        |

| 3    | Ceramic Capacitor 100 nF, 50 V, X7R | C1, C2 | 0603             | TDK             | C1608X7R1H104KT |

| 4    | Ceramic Capacitor 4.7 F, 6.3 V, X5R | C3, C4 | 0603             | ТDК             | C1608X5R0J475MT |

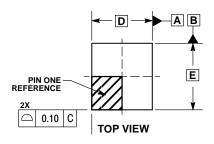

9 PIN FLIP CHIP 1.45x1.45x0.596 CASE 499AL

> b-Free strategy and soldering details, please downloo the

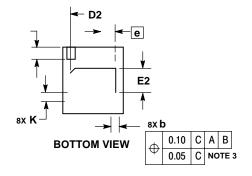

#### UDFN8 2x2.2, 0.5P CASE 506AV ISSUE C

DATE 26 JUN 2013

SCALE 4:1

- NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 mm FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi