# onse i

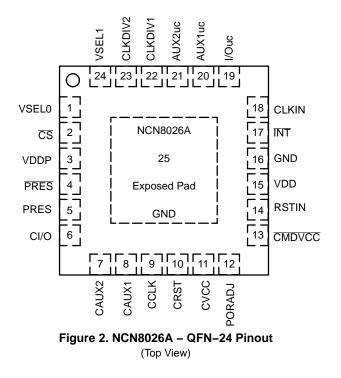

Figure 3. NCN8026A Block Diagram (QFN-24 Pin Numbering)

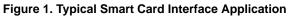

#### PIN FUNCTION AND DESCRIPTION

| Pin<br>(QFN24) | Name   | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6              | CI/O   | Input/<br>Output | This pin handles the connection to the serial I/O (C7) of the card connector. A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. A 11 k $\Omega$ (typical) pull up resistor to CVCC provides a High impedance state for the smart card I/O link.                                                                                                          |

| 7              | CAUX2  | Input/<br>Output | This pin handles the connection to the chip card's serial auxiliary AUX2 I/O pin (C8). A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. A 11 k $\Omega$ (typical) pull up resistor to CVCC provides a High impedance state for the smart card C8 pin.                                                                                                   |

| 8              | CAUX1  | Input/<br>Output | This pin handles the connection to the chip card's serial auxiliary AUX1 I/O pin (C4). A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. A 11 k $\Omega$ (typical) pull up resistor to CVCC provides a High impedance state for the smart card C4 pin.                                                                                                   |

| 9              | CCLK   | Output           | This pin is connected to the CLOCK card connector's pin (Chip card's pin C3). The Clock signal comes from the CLKIN input through clock dividers and level shifter.                                                                                                                                                                                                                                              |

| 10             | CRST   | Output           | This pin is connected to the chip card's RESET pin (C2) through the card connector. A level translator adapts the external Reset (RSTIN) signal to the smart card.                                                                                                                                                                                                                                               |

| 11             | CVCC   | Power<br>Output  | This pin is connected to the smart card power supply pin (C1). An internal low dropout regulator is programmable using the pins VSEL0 and VSEL1 to supply either 5 V or 3 V or 1.8 V output voltage. An external distributed ceramic capacitor ranging from 80 nF to 1.2 $\mu$ F recommended must be connected across CVCC and CGND. This set of capacitor (if distributed) must be low ESR (< 100 m $\Omega$ ). |

| 12             | PORADJ | Input            | Power-on reset threshold adjustment input pin for changing the reset threshold (V <sub>DD</sub> UVLO threshold) thanks to an external resistor power divider. Needs to be connected to ground when unused.                                                                                                                                                                                                       |

| 13             | CMDVCC | Input            | Command V <sub>CC</sub> pin. Activation sequence Enable/Disable pin (active Low). The activation sequence is enabled by toggling $\overline{CMDVCC}$ High to Low and when a card is present. When $\overline{CMDVCC}$ = High, the CVCC output is pulled low and the internal LDO is disabled unless the device has been latched by the $\overline{CS}$ pin.                                                      |

| 14             | RSTIN  | Input            | This Reset input connected to the host and referred to VDD (microcontroller side), is connected to the                                                                                                                                                                                                                                                                                                           |

#### **ATTRIBUTES**

| Characteristics                                                                                                                                                                             | Values                         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| ESD protection<br>Human Body Model (HBM) (Note 1)<br>Card Pins (card interface pins 4–11)<br>All Other Pins<br>Machine Model (MM)<br>Card Pins (card interface pins 4–11)<br>All Other Pins | 8 kV<br>2 kV<br>400 V<br>150 V |  |  |

| Moisture sensitivity (Note 2) QFN-24                                                                                                                                                        | Level 1                        |  |  |

| Flammability Rating Oxygen Index: 28 to 34                                                                                                                                                  | UL 94 V-0 @ 0.125 in           |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test                                                                                                                                     |                                |  |  |

1. Human Body Model (HBM), R = 1500  $\Omega,$  C = 100 pF.

2. For additional information, see Application Note AND8003/D.

#### MAXIMUM RATINGS (Note 3)

| Rating                                           | Symbol             | Value                                 | Unit |

|--------------------------------------------------|--------------------|---------------------------------------|------|

| Regulator Power Supply Voltage                   | V <sub>DDP</sub>   | –0.3 V <sub>DDP</sub> 5.5             | V    |

| Power Supply from Microcontroller Side           | V <sub>DD</sub>    | –0.3 V <sub>DD</sub> 5.5              | V    |

| External Card Power Supply                       | CVCC               | -0.3 CVCC 5.5                         | V    |

| Digital Input Pins                               | V <sub>in</sub>    | –0.3 V <sub>in</sub> V <sub>DD</sub>  | V    |

| Digital Output Pins (I/Ouc, AUX1uc, AUX2uc, INT) | V <sub>out</sub>   | –0.3 V <sub>out</sub> V <sub>DD</sub> | V    |

| Smart card Output Pins                           | V <sub>out</sub>   | -0.3 V <sub>out</sub> CVCC            | V    |

| Thermal Resistance Junction-to-Air QFN-2         | 4 R <sub>θJA</sub> | 90                                    | C/W  |

| Operating Ambient Temperature Range              | T <sub>A</sub>     | -40 to +85                            | С    |

| Operating Junction Temperature Range             | TJ                 | -40 to +125                           | С    |

| Maximum Junction Temperature                     | T <sub>Jmax</sub>  | +125                                  | С    |

| Storage Temperature Range                        | T <sub>stg</sub>   | -65 to + 150                          | С    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 3. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at  $T_A = +25$  C.

**POWER SUPPLY SECTION** (V<sub>DD</sub> = 3.3 V; V<sub>DDP</sub> = 5 V; T<sub>amb</sub> = 25 C; F<sub>CLKIN</sub> = 5 MHz)

Symbol

Rating

Min

#### HOST INTERFACE SECTION

SMART CARD INTERFACE SECTION CI/O, CAUX1, CAUX2, CCLK, CRST, PRES, PRES (V<sub>DD</sub> = 3.3 V; V<sub>DDP</sub> = 5 V; T<sub>amb</sub> = 25

**SMART CARD INTERFACE SECTION** CI/O, CAUX1, CAUX2, CCLK, CRST, PRES,  $\overline{PRES}$  (V<sub>DD</sub> = 3.3 V; V<sub>DDP</sub> = 5 V; T<sub>amb</sub> = 25 C; F<sub>CLKIN</sub> = 5 MHz)

| Symbol | Rating | Min | Тур | Мах | Unit |

|--------|--------|-----|-----|-----|------|

|        |        |     |     |     |      |

$|I_{\rm H}|$

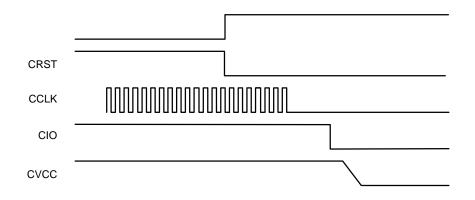

Finally the Reset level shifter is enabled (typically 2  $\mu$ s after clock channel) (t4)

The clock can also be applied to the card using a **RSTIN mode** allowing controlling the clock starting by setting RSTIN Low (Figure 4). Before running the activation sequence, that is before setting Low <u>CMDVCC</u> RSTIN is set High. The following sequence is applied:

The Smart Card Interface is enable by setting CMDVCC LOW (RSTIN is High).

Between t2 (Figure 4) and t5 = 240  $\mu$ s, RSTIN is reset to LOW and CCLK will start precisely at this moment allowing a precise count of clock cycles before toggling CRST Low to High for ATR (Answer To Reset) request.

CRST remains LOW until 240  $\mu$ s; after t5 = 240  $\mu$ s CRST is enabled and is the copy of RSTIN which has no more control on the clock. If controlling the clock with RSTIN is not necessary (**Normal Mode**), then  $\overline{\text{CMDVCC}}$  can be set LOW with RSTIN LOW. In that case, CLK will start minimum 2 µs after the transition on I/O (Figure 5), and to obtain an ATR, CRST can be set High by RSTIN also about 2 µs after the clock channel activation (T<sub>act</sub>).

The internal activation sequence activates the different channels according to a specific hardware built in sequencing internally defined but at the end the actual activation

#### SMART CARD POWER-DOWN

When the communication session is completed the NCN8026A runs a deactivation sequence by setting High CMDVCC. The below power down sequence is executed:

CRST is forced to Low CCLK is set Low 12 µs after CRST. CI/O, CAUX1 and CAUX2 are pulled Low Finally CVCC supply can be shut off.

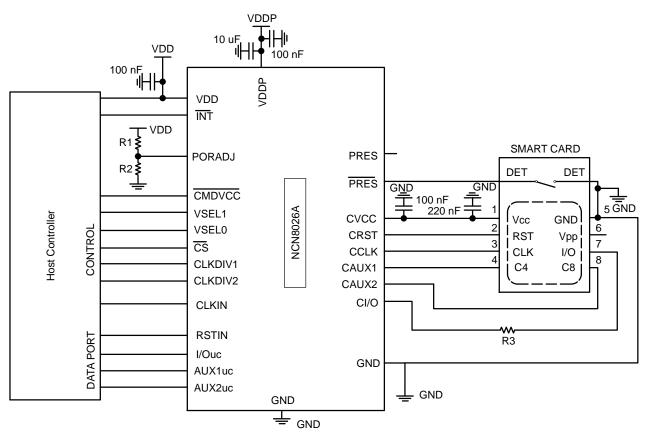

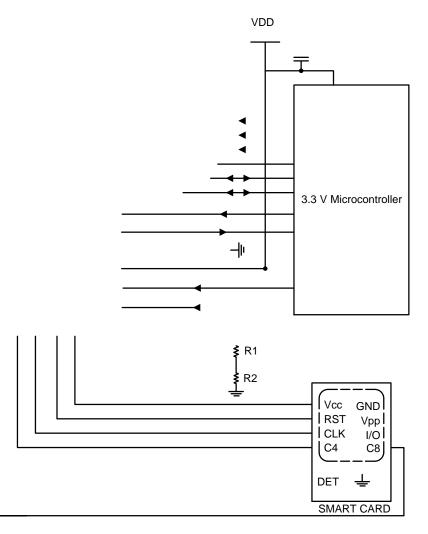

## **APPLICATION SCHEMATIC**

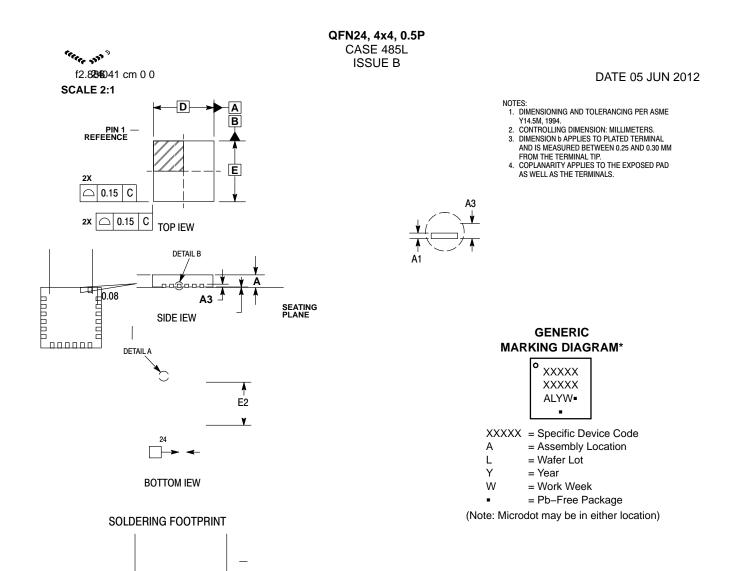

2.90

DIMENSIONS: MILLIMETERS

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi