# High Speed Dual-Channel, Ceramic Digital Isolator

# **Product Preview**

# **NCID9200**

#### Description

The NCID9200 is a galvanically isolated high–speed dual–channel digital isolator. This device supports isolated communications thereby allowing digital signals to communicate between systems without conducting ground loops or hazardous voltages.

It utilizes **onsemi**'s patented galvanic off-chip capacitor isolation technology and optimized IC design to achieve high insulation and high noise immunity, characterized by high common mode rejection and power supply rejection specifications. The thick ceramic substrate yields capacitors with  $\sim\!25$  times the thickness of thin film on-chip capacitors and coreless transformers. The result is a combination of the electrical performance benefits that digital isolators offer with the safety reliability of a  $>\!0.5$  mm insulator barrier similar to what has historically been offered by optocouplers.

The device is housed in a 16-pin wide body small outline package.

#### **Features**

- ∉ Off-Chip Capacitive Isolation to Achieve Reliable High Voltage Insulation

- ↓ DTI (Distance Through Insulation): Ø 0.5 mm

- ↓ Maximum Working Insulation Voltage: 2000 V<sub>peak</sub>

- ∉ 100 kV/ s Minimum Common Mode Rejection

- ∉ 8 mm Creepage and Clearance Distance to Achieve Reliable High Voltage Insulation

- **∉** Over Temperature Detection

- ♥ NCIV Prefix for Automotive and Other Applications Requiring

Unique Site and Control Change Requirements; AEC-Q100

Qualified and PPAP Capable (Pending)

# **PIN CONFIGURATION**

Figure 1. Pin and Channel Configuration

## **SPECIFICATIONS**

## TRUTH TABLE (Note 1)

|   | V <sub>INX</sub> | V <sub>DDI</sub> | $V_{DDO}$ | V <sub>OX</sub> | Comment          |

|---|------------------|------------------|-----------|-----------------|------------------|

| Ī | Н                | Power Up         | Power Up  | Н               | Normal Operation |

| Ī | L                | Power Up         | Power Up  | L               |                  |

# **ABSOLUTE MAXIMUM RATINGS** ( $T_A = 25 \mbox{\em V} C$ unless otherwise specified)

| Symbol           | Parameter                                                     | Value        | Unit |

|------------------|---------------------------------------------------------------|--------------|------|

| T <sub>STG</sub> | Storage Temperature                                           | -55 to +150  | ∀C   |

| T <sub>OPR</sub> | Operating Temperature                                         | -40 to +125  | ∀C   |

| TJ               | Junction Temperature                                          | -40 to +150  | ∀C   |

| T <sub>SOL</sub> | Lead Solder Temperature (Refer to Reflow Temperature Profile) | 260 for 10 s | ∀C   |

| V <sub>DD</sub>  | Supply Voltage (V <sub>DDx</sub> )                            |              | •    |

**ELECTRICAL CHARACTERISTICS** Apply over all recommended conditions,  $T_A = -40 \text{ VC}$  to +125 VC,  $V_{DD1} = V_{DD2} = 2.5 \text{ V}$  to 5.5 V, unless otherwise specified. All typical values are measured at  $T_A = 25 \text{ VC}$ .

| Symbol            | Parameter                         | Conditions                                       | Min                    | Тур                    | Max                    | Unit | Figure |

|-------------------|-----------------------------------|--------------------------------------------------|------------------------|------------------------|------------------------|------|--------|

| V <sub>OH</sub>   | High Level Output Voltage         | $V_{DD} = 5 \text{ V}, I_{OH} = -4 \text{ mA}$   | V <sub>DDO</sub> – 0.4 | V <sub>DDO</sub> – 0.1 | -                      | V    | 7      |

|                   |                                   | $V_{DD} = 3.3 \text{ V}, I_{OH} = -2 \text{ mA}$ |                        |                        |                        |      |        |

|                   |                                   | $V_{DD} = 2.5 \text{ V}, I_{OH} = -1 \text{ mA}$ |                        |                        |                        |      |        |

| V <sub>OL</sub>   | Low Level Output Voltage          | $V_{DD} = 5 \text{ V}, I_{OL} = 4 \text{ mA}$    | -                      | 0.1                    | 0.4                    | V    | 8      |

|                   |                                   | $V_{DD} = 3.3 \text{ V}, I_{OL} = 2 \text{ mA}$  |                        |                        |                        |      |        |

|                   |                                   | V <sub>DD</sub> = 2.5 V, I <sub>OL</sub> = 1 mA  |                        |                        |                        |      |        |

| V <sub>INT+</sub> | Rising Input Voltage<br>Threshold |                                                  | -                      | -                      | 0.7 Δ V <sub>DDI</sub> | V    |        |

| V <sub>INT</sub>  | •                                 | 1                                                | •                      | •                      |                        | 1    | •      |

SUPPLY CURRENT CHARACTERISTICS (continued) Apply over all recommended conditions,  $T_A = -40 \text{ }\%\text{C}$  to +125 %C unless otherwise specified. All typical values are measured at  $T_A = 25 \text{ }\%\text{C}$ .

| Symbol           | Parameter                    | Conditions                                                                                                            | Min | Тур      | Max  | Unit | Figure |

|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|----------|------|------|--------|

| I <sub>DD1</sub> | AC Supply                    | $V_{DD} = 5 \text{ V}, \text{ EN} = 5 \text{ V}, \text{ C}_{L} = 15 \text{ pF},$                                      | -   | 8.3      | 13.6 | mA   | 3, 4   |

| $I_{DD2}$        | Current 20 Mbps              | V <sub>IN</sub> = 5 V Square Wave                                                                                     |     | 14.2     | 15.2 |      |        |

| I <sub>DD1</sub> | AC Supply<br>Current 20 Mbps | $V_{DD} = 3.3 \text{ V}, \text{ EN} = 3.3 \text{ V}, C_L = 15 \text{ pF}, V_{IN} = 3.3 \text{ V} \text{ Square Wave}$ |     | 8.2      | 12.2 |      |        |

| $I_{DD2}$        |                              | V <sub>IN</sub> = 3.3 v Square wave                                                                                   |     | 11.9     | 13.2 |      |        |

| I <sub>DD1</sub> |                              | V <sub>DD</sub> = 2.5 V, EN = 2.5 V, C <sub>L</sub> = 15 pF,<br>V <sub>IN</sub> = 2.5 V Square Wave                   |     | 8.1 11.6 | 11.6 |      |        |

| I <sub>DD2</sub> |                              |                                                                                                                       |     | 11.1     | 12.7 |      |        |

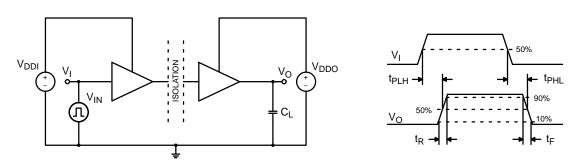

## **SWITCHING CHARACTERISTICS**

Apply over all recommended conditions,  $T_A = -40 \text{ VC}$  to +125 VC unless otherwise specified. All typical values are measured at  $T_A = 25 \text{ VC}$ .

| Symbol           | Parameter | Conditions | Min | Тур | Max | Unit | Figure |

|------------------|-----------|------------|-----|-----|-----|------|--------|

| t <sub>PHL</sub> |           |            |     |     |     |      |        |

|                  |           |            |     |     |     |      |        |

|                  |           |            |     |     |     |      |        |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3. Supply Current vs. Data Rate (No Load)

Figure 4. Supply Current vs. Data Rate (Load = 15 pF)

Figure 5. Supply Voltage UVLO Threshold vs.

Ambient Temperature

Figure 6. Propagation Delay vs. Ambient Temperature

## **TEST CIRCUITS**

Figure 9.  $\rm V_{IN}$  to  $\rm V_{O}$  Propagation Delay Test Circuit and Waveform

Figure 10. Common Mode Transient Immunity Test Circuit

Figure 14. 4-Layer PCB for Digital Isolator

Figure 15. Placement of Bypass Capacitors