# 3.3 V/5 V Programmable PLL Synthesized Clock Generator

# 50 MHz to 800 MHz

# NBC12430, NBC12430A

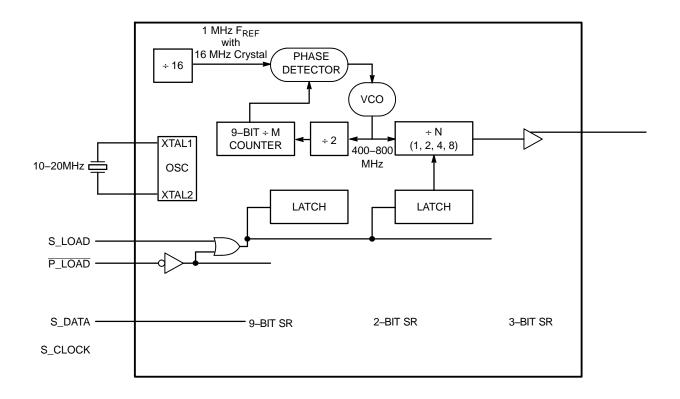

The NBC12430 and NBC12430A are general purpose, PLL based synthesized clock sources. The VCO will operate over a frequency range of 400 MHz to 800 MHz. The VCO frequency is sent to the N-output divider, where it can be configured to provide division ratios of 1, 2, 4, or 8. The VCO and output frequency can be programmed using the parallel or serial interfaces to the configuration logic. Output frequency steps of 250 kHz, 500 kHz, 1.0 MHz, 2.0 MHz can be achieved using a 16 MHz crystal, depending on the output dividers settings. The PLL loop filter is fully integrated and does not require any external components.

#### **Features**

- Best-in-Class Output Jitter Performance, ±20 ps Peak-to-Peak

- 50 MHz to 800 MHz Programmable Differential PECL Outputs

- Fully Integrated Phase–Lock–Loop with Internal Loop Filter

- Parallel Interface for Programming Counter and Output Dividers During Powerup

- Minimal Frequency Overshoot

- Serial 3-Wire Programming Interface

- Crystal Oscillator Interface

- Operating Range:  $V_{CC} = 3.135 \text{ V}$  to 5.25 V

- CMOS and TTL Compatible Control Inputs

- Pin and Function Compatible with Motorola MC12430 and MPC9230

- 0°C to 70°C Ambient Operating Temperature (NBC12430)

- -40°C to 85°C Ambient Operating Temperature (NBC12430A)

- Pb-Free Packages are Available

#### MARKING DIAGRAMS

LQFP-32 FA SUFFIX CASE 561AB

x = Blank or A

A = Assembly Location

WL, L = Wafer Lot YY, Y = Year WW, W = Work Week G or ■ = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 16 of this data sheet.

1

Figure 1. Block Diagram

The following gives a brief description of the functionality of the NBC12430 and NBC12430A Inputs and Outputs. Unless explicitly stated, all inputs are CMOS/TTL compatible with either pullup or pulldown resistors. The PECL outputs are capable of driving two series terminated 50  $\Omega$  transmission lines on the incident edge.

## **Table 3. PIN FUNCTION DESCRIPTION**

| Pin Name     | Function                                                    | Description                                                                                                                                                                                                                              |

|--------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUTS       |                                                             |                                                                                                                                                                                                                                          |

| XTAL1, XTAL2 | Crystal Inputs                                              | These pins form an oscillator when connected to an external series–resonant crystal.                                                                                                                                                     |

| S_LOAD*      | CMOS/TTL Serial Latch Input<br>(Internal Pulldown Resistor) | This pin loads the configuration latches with the contents of the shift registers. The latches will be transparent when this signal is HIGH; thus, the data must be stable on the HIGH-to-LOW transition of S_LOAD for proper operation. |

| S_DATA*      | CMOS/TTL Serial Data Input (Internal Pulldown Resistor)     | This pin acts as the data input to the serial configuration shift registers.                                                                                                                                                             |

S\_CLOCK\*

# Table 4. ATTRIBUTES

| Characteristics                                                    | Value                             |

|--------------------------------------------------------------------|-----------------------------------|

| Internal Input Pulldown Resistor                                   | 75 kΩ                             |

| Internal Input Pullup Resistor                                     | 37.5 kΩ                           |

| ESD Protection Human Body Model Machine Model Charged Device Model | > 2 kV<br>> 150 V<br>> 1 kV       |

| Moisture Sensitivity (Note 1) LQFP QFN                             | Pb-Free Pkg<br>Level 2<br>Level 1 |

| Flammability Rating Oxygen Index: 28 to 34'                        | UL 94 V-0 @ 0.125 in              |

| Transistor Count                                                   | 2011                              |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test             | •                                 |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

# **Table 5. MAXIMUM RATINGS**

| Symbol           | Parameter                   | Condition 1         | Condition 2         | Rating    | Units    |

|------------------|-----------------------------|---------------------|---------------------|-----------|----------|

| V <sub>CC</sub>  | Positive Supply             | GND = 0 V           |                     | 6         | V        |

| VI               | Input Voltage               | GND = 0 V           | $V_{I} \leq V_{CC}$ | 6         | V        |

| l <sub>out</sub> | Output Current              | Continuous<br>Surge |                     | 50<br>100 | mA<br>mA |

| T <sub>A</sub>   | Operating Temperature Range | •                   | -                   | •         | -        |

**Table 8. AC CHARACTERISTICS** ( $V_{CC} = 3.135 \text{ V to } 5.25 \text{ V} \pm 5\%$ ,  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  (NBC12430),  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (NBC12430A))

| Symbol                          | Characte                   | ristic                                                   | Condition                                                                                      | Min            | Max             | Unit |

|---------------------------------|----------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------|-----------------|------|

| F <sub>MAXI</sub>               | Maximum Input Frequency    | S_CLOCK<br>XTAL Oscillator<br>FREF_EXT (Note 8)          | (Note 6)                                                                                       | 10<br>10       | 10<br>20<br>100 | MHz  |

| F <sub>MAXO</sub>               | Maximum Output Frequen     | cy VCO (Internal)<br>F <sub>OUT</sub>                    |                                                                                                | 400<br>50      | 800<br>800      | MHz  |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time      |                                                          |                                                                                                |                | 10              | ms   |

| <sup>t</sup> jitter(pd)         | Period Jitter (RMS)        | (1σ)                                                     | $50 \text{ MHz} \le f_{OUT} < 100 \text{ MHz}$ $100 \text{ MHz} \le f_{OUT} < 800 \text{ MHz}$ |                | 8<br>5          | ps   |

| tjitter(cyc-cyc)                | Cycle-to-Cycle Jitter (Pea | k-to-Peak) (8σ)                                          | $50 \text{ MHz} \le f_{OUT} < 100 \text{ MHz}$ $100 \text{ MHz} \le f_{OUT} < 800 \text{ MHz}$ |                | ±40<br>±20      | ps   |

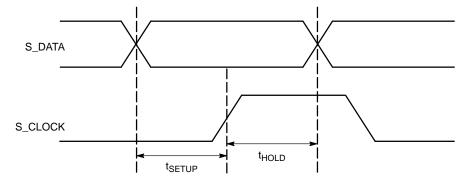

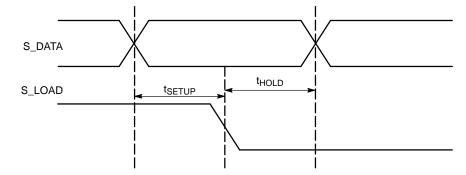

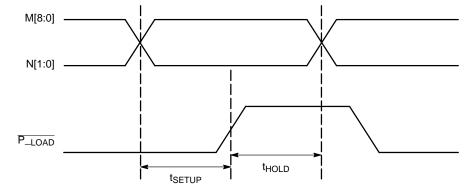

| t <sub>s</sub>                  | Setup Time                 | S_DATA to S_CLOCK<br>S_CLOCK to S_LOAD<br>M, N to P_LOAD |                                                                                                | 20<br>20<br>20 |                 | ns   |

| t <sub>h</sub>                  | Hold Time                  | S_DATA to S_CLOCK<br>M, N to P_LOAD                      |                                                                                                | 20<br>20       |                 | ns   |

| tpw <sub>MIN</sub>              | Minimum Pulse Width        | S_LOAD<br>P_LOAD                                         |                                                                                                | 50<br>50       |                 | ns   |

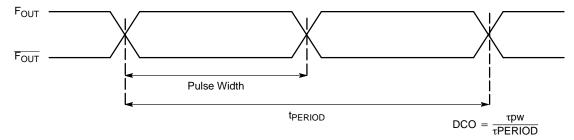

| DCO                             | Output Duty Cycle          |                                                          |                                                                                                | 47.5           | 52.5            | %    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall           | F <sub>OUT</sub>                                         | 20%-80%                                                                                        | 175            | 425             | ps   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

<sup>6. 10</sup> MHz is the maximum frequency to load the feedback divide registers. S\_CLOCK can be switched at higher frequencies when used as a test clock in TEST\_MODE 6.

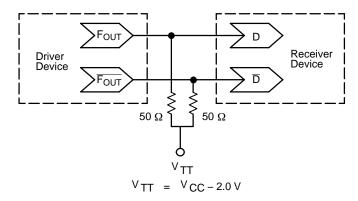

F<sub>OUT/</sub>F<sub>OUT</sub> and TEST outputs are terminated through a 50 Ω resistor to V<sub>CC</sub> – 2.0 V.

Maximum frequency on FREF\_EXT is a function of setting the appropriate M counter value for the VCO to operate within the valid range of 400 MHz ≤ f<sub>VCO</sub> ≤ 800 MHz. (See Table 11).

#### **APPLICATIONS INFORMATION**

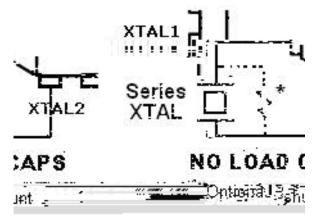

#### Using the On-Board Crystal Oscillator

The NBC12430 and NBC12430A feature a fully integrated on-board crystal oscillator to minimize system implementation costs. The oscillator is a series resonant, multivibrator type design as opposed to the more common parallel resonant oscillator design. The series resonant design provides better stability and eliminates the need for large load capacitors per Figure 7 (do not use crystal load caps). The oscillator is totally self contained so that the only external component required is the crystal. As the oscillator is somewhat sensitive to loading on its inputs, the user is advised to mount the crystal as close to the device as possible to avoid any board level parasitics. To facilitate co-location, surface mount crystals are recommended, but not required. Because the series resonant design is affected by capacitive loading on the crystal terminals, loading variation introduced by crystals from different vendors could be a potential issue. For crystals with a higher shunt capacitance, it may be required to place a resistance, optional R<sub>shunt</sub>, across the terminals to suppress the third harmonic. Although typically not required, it is a good idea to layout the PCB with the provision of adding this external resistor. The resistor value will typically be between 500  $\Omega$  and 1 k $\Omega$ .

Figure 7. Crystal Application

The oscillator circuit is a series resonant circuit and thus, for optimum performance, a series resonant crystal should be used. Unfortunately, most crystals are characterized in a parallel resonant mode. Fortunately, there is no physical difference between a series resonant and a parallel resonant crystal. The difference is purely in the way the devices are characterized. As a result, a parallel resonant crystal can be used with the device with only a minor error in the desired frequency. A parallel resonant mode crystal used in a series resonant

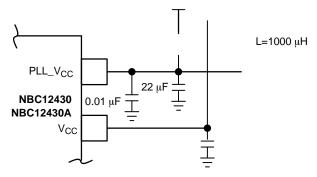

impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the bandwidth of the PLL.

Figure 8. Power Supply Filter

Figure 13. Setup and Hold

Figure 14. Setup and Hold

Figure 15. Setup and Hold

Figure 16. Output Duty Cycle

Figure 17. Typical Termination for Output Driver and Device Evaluation (See Application Note <u>AND8020</u> – Termination of ECL Logic Devices.)

#### **ORDERING INFORMATION**

| Device        | Package              | Shipping <sup>†</sup> |

|---------------|----------------------|-----------------------|

| NBC12430FAR2G | LQFP-32<br>(Pb-Free) | 2000 / Tape & Reel    |

| NBC12430AMNG  | QFN-32<br>(Pb-Free)  | 74 Units / Tube       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <a href="https://example.com/BRD8011/D">BRD8011/D</a>.

## **Resource Reference of Application Notes**

AN1405/D - ECL Clock Distribution Techniques

AN1406/D - Designing with PECL (ECL at +5.0 V)

AN1503/D - ECLinPS™ I/O SPiCE Modeling Kit

AN1504/D - Metastability and the ECLinPS Family

AN1568/D - Interfacing Between LVDS and ECL

AN1672/D - The ECL Translator Guide

AND8001/D - Odd Number Counters Design

AND8002/D - Marking and Date Codes

AND8020/D - Termination of ECL Logic Devices

AND8066/D - Interfacing with ECLinPS

AND8090/D - AC Characteristics of ECL Devices

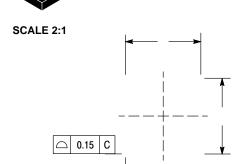

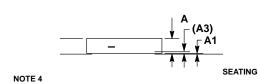

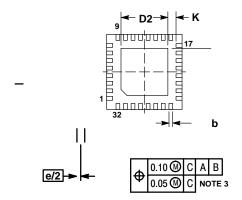

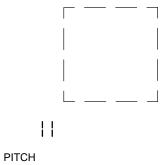

# **MECHANICAL CASE OUTLINE**

**PACKAGE DIMENSIONS**

**DATE 23 OCT 2013**

# MAX 0.80 1.00 A1 --- 0.05 A3 0.20 REF b 0.18 0.30 D 5.00 BSC D2 2.95 3.25 E 5.00 BSC E2 2.95 | 3.25 e 0.50 BSC K 0.20 --L 0.30 0.50 L1 --- 0.15

XXXXXXX

XXXXXXX

AWLYYWW=

Free indicator, "G" or

#### **RECOMMENDED**

DIMENSION: MILLIMETERS

| DOCUMENT NUMBER: | 98AON20032D |  |

|------------------|-------------|--|

|                  |             |  |

1, 0,30 1,40 1,45  $\|\ \|\ \|\ \|\ \|\ \|$ A2 ,

0.45

SEE DETAIL B

A1