Thank you for your interest in **onsemi** products.

Your technical document begins on the following pages.

# Your Feedback is Important to Us!

Please take a moment to participate in our short survey.

At **onsemi**, we are dedicated to delivering technical content that best meets your needs.

# Help Us Improve - Take the Survey

This survey is intended to collect your feedback, capture any issues you may encounter, and to provide improvements you would like to suggest.

# We look forward to your feedback.

To learn more about **onsemi**, please visit our website at **www.onsemi.com**

# 3.3 V/5 V Programmable PLL Synthesized Clock Generator

#### 25 MHz to 400 MHz

## NBC12429, NBC12429A

#### Description

The NBC12429 and NBC12429A are general purpose, Phase–Lock–Loop (PLL) based synthesized clock sources. The VCO will operate over a frequency range of 200 MHz to 400 MHz. The VCO frequency is sent to the N–output divider, where it can be configured to provide division ratios of 1, 2, 4, or 8. The VCO and output frequency can be programmed using the parallel or serial interfaces to the configuration logic. Output frequency steps of 125 kHz, 250 kHz, 500 kHz, or 1.0 MHz can be achieved using a 16 MHz crystal, depending on the output dividers. The PLL loop filter is fully integrated and does not require any external components.

#### **Features**

- Best-in-Class Output Jitter Performance, ±20 ps Peak-to-Peak

- 25 MHz to 400 MHz Programmable Differential PECL Outputs

- Fully Integrated Phase–Lock–Loop with Internal Loop Filter

- Parallel Interface for Programming Counter and Output Dividers During Powerup

- Minimal Frequency Overshoot

- Serial 3-Wire Programming Interface

- Crystal Oscillator Interface

- Operating Range:  $V_{CC} = 3.135 \text{ V}$  to 5.25 V

- CMOS and TTL Compatible Control Inputs

- Pin and Function Compatible with Motorola MC12429 and MPC9229

- 0°C to 70°C Ambient Operating Temperature (NBC12429)

- -40°C to 85°C Ambient Operating Temperature (NBC12429A)

- These Devices are Pb-Free and are RoHS Compliant

LQFP-32 FA SUFFIX CASE 561AB

#### **MARKING DIAGRAMS**

The following gives a brief description of the functionality of the NBC12429 and NBC12429A Inputs and Outputs. Unless explicitly stated, all inputs are CMOS/TTL compatible with either pullup or pulldown resistors. The PECL outputs are capable of driving two series terminated 50  $\Omega$  transmission lines on the incident edge.

#### **Table 3. PIN FUNCTION DESCRIPTION**

| Pin Name     | Function                                                    | Description                                                                                                                                                                                                                                           |

|--------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUTS       |                                                             |                                                                                                                                                                                                                                                       |

| XTAL1, XTAL2 | Crystal Inputs                                              | These pins form an oscillator when connected to an external series–resonant crystal.                                                                                                                                                                  |

| S_LOAD*      | CMOS/TTL Serial Latch Input<br>(Internal Pulldown Resistor) | This pin loads the configuration latches with the contents of the shift registers. The latches will be transparent when this signal is HIGH; thus, the data must be stable on the HIGH-to-LOW transition of S_LOAD for proper operation.              |

| S_DATA*      | CMOS/TTL Serial Data Input (Internal Pulldown Resistor)     | This pin acts as the data input to the serial configuration shift registers.                                                                                                                                                                          |

| S_CLOCK*     | CMOS/TTL Serial Clock Input (Internal Pulldown Resistor)    | This pin serves to clock the serial configuration shift registers. Data from S_DATA is sampled on the rising edge.                                                                                                                                    |

| P_LOAD**     | CMOS/TTL Parallel Latch Input<br>(Internal Pullup Resistor) | This pin loads the configuration latches with the contents of the parallel inputs. The latches will be transparent when this signal is LOW; therefore, the parallel data must be stable on the LOW–to–HIGH transition of P_LOAD for proper operation. |

**Table 4. ATTRIBUTES**

| Characteristics                                                    | Value                       |

|--------------------------------------------------------------------|-----------------------------|

| Internal Input Pulldown Resistor                                   | 75 kΩ                       |

| Internal Input Pullup Resistor                                     | 37.5 kΩ                     |

| ESD Protection Human Body Model Machine Model Charged Device Model | > 2 kV<br>> 150 V<br>> 1 kV |

| Moisture Sensitivity (Note 1)                                      | Pb-Free Pkg                 |

| LQFP<br>QFN                                                        | Level 2<br>Level 1          |

| Flammability Rating Oxygen Index: 28 to 34                         | UL 94 V-0 @ 0.125 in        |

| Transistor Count                                                   | 2035                        |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test             | •                           |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

#### **Table 5. MAXIMUM RATINGS**

| Symbol            | Parameter                                      | Condition 1         | Condition 2         | Rating                | Unit     |

|-------------------|------------------------------------------------|---------------------|---------------------|-----------------------|----------|

| V <sub>CC</sub>   | Positive Supply                                | GND = 0 V           |                     | 6                     | V        |

| VI                | Input Voltage                                  | GND = 0 V           | $V_{I} \leq V_{CC}$ | 6                     | V        |

| l <sub>out</sub>  | Output Current                                 | Continuous<br>Surge |                     | 50<br>100             | mA<br>mA |

| T <sub>A</sub>    | Operating Temperature Range NBC12429 NBC12429A |                     |                     | 0 to 70<br>-40 to +85 | °C       |

| T <sub>stg</sub>  | Storage Temperature Range                      |                     |                     | -65 to +150           | °C       |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction-to-Ambient)       | 0 lfpm<br>500 lfpm  | LQFP-32<br>LQFP-32  | 80<br>55              | °C/W     |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case)          | Standard Board      | LQFP-32             | 12 to 17              | °C/W     |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction-to-Ambient)       | 0 lfpm<br>500 lfpm  | QFN-32<br>QFN-32    | 31<br>27              | °C/W     |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case)          | 2S2P                | QFN-32              | 12                    | °C/W     |

| T <sub>sol</sub>  | Wave Solder (Pb-Free)                          | <3 sec @ 260°C      |                     | 265                   | °C       |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **Table 6. DC CHARACTERISTICS** ( $V_{CC} = 3.3 \text{ V} \pm 5\%$ ; $T_A = 0^{\circ}\text{C}$ to $70^{\circ}\text{C}$ (NBC12429), $T_A = -40^{\circ}\text{C}$ to $85^{\circ}\text{C}$ (NBC12429A))

| Symb                             | Characteristic     | Condition               | Min | Тур | Max | Unit |

|----------------------------------|--------------------|-------------------------|-----|-----|-----|------|

| V <sub>IH</sub><br>LVCMO<br>LVTT | Input HIGH Voltage | V <sub>CC</sub> = 3.3 V | 2.0 |     |     | V    |

**Table 8. AC CHARACTERISTICS** ( $V_{CC} = 3.125 \text{ V}$  to 5.25 V;  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  (NBC12429),  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (NBC12429A)) (Note 6)

| Symbol                  | Characteristic                                                           |                                    | Condition                                                                                                                                                                                                                                                                                       | Min       | Max                                   | Unit              |

|-------------------------|--------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|-------------------|

| F <sub>MAXI</sub>       | Maximum Input Frequency                                                  | S_CLOCK<br>Xtal Oscillator         | (Note 7)                                                                                                                                                                                                                                                                                        | 10        | 10<br>20                              | MHz               |

| F <sub>MAXO</sub>       | Maximum Output Frequency                                                 | VCO (Internal)<br>F <sub>OUT</sub> |                                                                                                                                                                                                                                                                                                 | 200<br>25 | 400<br>400                            | MHz               |

| <sup>t</sup> jitter(pd) | Period Jitter @ 3.3 V<br>10000 WFMS<br>(See Table 13 for Typical Values) |                                    | 25 MHz < f <sub>OUT</sub> < 100 MHz, M = 200<br>25 MHz < f <sub>OUT</sub> < 100 MHz, M = 300<br>25 MHz < f <sub>OUT</sub> < 100 MHz, M = 400<br>100 MHz < f <sub>OUT</sub> < 400 MHz, M = 200<br>100 MHz < f <sub>OUT</sub> < 400 MHz, M = 300<br>100 MHz < f <sub>OUT</sub> < 400 MHz, M = 400 |           | 25<br>9.0<br>6.0<br>9.0<br>5.0<br>4.0 | ps <sub>RMS</sub> |

|                         |                                                                          |                                    | 25 MHz < f <sub>OUT</sub> < 100 MHz, M = 200<br>25 MHz < f <sub>OUT</sub><br>25 MHz < f                                                                                                                                                                                                         | •         | •                                     |                   |

**Table 8. AC CHARACTERISTICS** ( $V_{CC} = 3.125 \text{ V}$  to 5.25 V;  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  (NBC12429),  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (NBC12429A)) (Note 6)

| Symbol                          | Charac              | cteristic                                                | Condition | Min            | Max  | Unit |

|---------------------------------|---------------------|----------------------------------------------------------|-----------|----------------|------|------|

| t <sub>s</sub>                  | Setup Time          | S_DATA to S_CLOCK<br>S_CLOCK to S_LOAD<br>M, N to P_LOAD |           | 20<br>20<br>20 |      | ns   |

| t <sub>h</sub>                  | Hold Time           | S_DATA to S_CLOCK<br>M, N to P_LOAD                      |           | 20<br>20       |      | ns   |

| t <sub>pwMIN</sub>              | Minimum Pulse Width | S_LOAD<br>P_LOAD                                         |           | 50<br>50       |      | ns   |

| DCO                             | Output Duty Cycle   |                                                          |           | 47.5           | 52.5 | %    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall    | F <sub>OUT</sub>                                         | 20%-80%   | 175            | 425  | ps   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

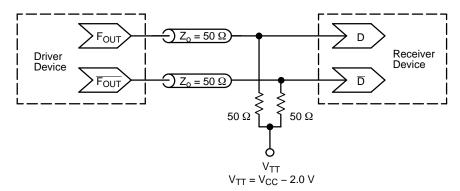

<sup>6.</sup> F<sub>OUT</sub>/F<sub>OUT</sub> outputs are terminated through a 50 Ω resistor to V<sub>CC</sub> – 2.0 V.

7. 10 MHz is the maximum frequency to load the feedback divide registers. S\_CLOCK can be switched at higher frequencies when used as a test clock in TEST\_MODE 6.

#### PROGRAMMING INTERFACE

Programming the NBC12429 and NBC12429A is accomplished by properly configuring the internal dividers to produce the desired frequency at the outputs. The output frequency can by represented by this formula:

FOUT =

$$(F\chi TAL \div 16) \times M \div N$$

(eq. 1)

where  $F_{XTAL}$  is the crystal frequency, M is the loop divider modulus, and N is the output divider modulus. Note that it is possible to select values of M such that the PLL is unable to achieve loop lock. To avoid this, always make sure that M is selected to be  $200 \le M \le 400$  for a 16 MHz input reference.

Assuming that a 16 MHz reference frequency is used the above equation reduces to:

$$FOUT = M \div N$$

(eq. 2)

Substituting the four values for N (1, 2, 4, 8) yields:

**Table 10. Programmable Output Divider Function**

| N1 | N0 | N Divider | F <sub>OUT</sub> | Output<br>Frequency<br>Range (MHz)* | F <sub>OUT</sub><br>Step |

|----|----|-----------|------------------|-------------------------------------|--------------------------|

| 0  | 0  | ÷1        | М                | 200-400                             |                          |

Most of the signals available on the TEST output pin are useful only for performance verification of the device itself. However, the PLL bypass mode may be of interest at the board level for functional debug. When T[2:0] is set to 110, the device is placed in PLL bypass mode. In this mode the S\_CLOCK input is fed directly into the M and N dividers. The N divider drives the F<sub>OUT</sub> differential pair and the M counter drives the TEST output pin. In this mode the S\_CLOCK input could be used for low speed board level functional test or debug. Bypassing the PLL and driving F<sub>OUT</sub> directly gives the user more control on the test clocks

## **APPLICATIONS INFORMATION**

| Using the | On-Board | Crystal | Oscillator |

|-----------|----------|---------|------------|

|-----------|----------|---------|------------|

The NBC12429 and NBC12429A feature a fully

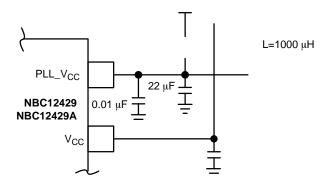

increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the bandwidth of the PLL.

Figure 8. Power Supply Filter

### Table 13. TYPICAL JITTER PERFORMANCE, 3.3 V, 25°C with 16 MHz Crystal Input at Selected M and N Values

|         |     |     | ,   |     |     | ,   |     |     |     |     |     |     |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| M Value | 200 | 200 | 200 | 200 | 300 | 300 | 300 | 300 | 400 | 400 | 400 | 400 |

| N Value | 1   | 2   | 4   | 8   | 1   | 2   | 4   | 8   | 1   | 2   | 4   | 8   |

| <br>· _ | _   | _   | _   | _   | ='  | ='  | =   | =   | -   |     |     |     |

JITTER

Figure 14. Typical Termination for Output Driver and Device Evaluation (See Application Note <u>AND8020/D</u> – Termination of ECL Logic Devices.)

#### **Resource Reference of Application Notes**

AN1405/D – ECL Clock Distribution Techniques

AN1406/D – Designing with PECL (ECL at +5.0 V)

AN1503/D – ECLinPS™ I/O SPiCE Modeling Kit

AN1504/D – Metastability and the ECLinPS Family

AN1568/D – Interfacing Between LVDS and ECL

AN1672/D - The ECL Translator Guide

AND8001/D - Odd Number Counters Design

AND8002/D - Marking and Date Codes

AND8020/D - Termination of ECL Logic Devices

AND8066/D - Interfacing with ECLinPS

AND8090/D - AC Characteristics of ECL Devices