# 3.3 V/5 V, 50 MHz to 200 MHz PECL Clock Synthesizer

**NB4N507A**

Figure 2. NB4N507A Logic Diagram

### Table 3. PIN DESCRIPTION

| Pin #<br>SOIC-16  | Name            | I/O                       | Description                                                                                                                                                                                                 |

|-------------------|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | X1/CLK          | Crystal Input             | Crystal or Clock Input                                                                                                                                                                                      |

| 2,3               | V <sub>DD</sub> | Power Supply              | Positive Supply Voltage (3.0 V to 5.5 V)                                                                                                                                                                    |

| 4                 | S1              | Tri-Level Input           | Multiplier Select Pin; When Left Open, Defaults to V_DD $\div$ 2                                                                                                                                            |

| 5,6               | GND             | Power Supply              | Negative Supply Voltage                                                                                                                                                                                     |

| 7,10,11,12,<br>15 | NC              | No Connect                | Pin 10 does not require an external resistor. The NB4N507A will function with or without a resistor on Pin 10.                                                                                              |

| 8                 | CLKOUT          | PECL Output*              | Non-inverted differential PECL clock output.                                                                                                                                                                |

| 9                 | CLKOUT          | PECL Output*              | Inverted differential PECL clock output.                                                                                                                                                                    |

| 13                | OE              | (LV)CMOS/(LV)TTL<br>Input | Output Enable for the CLKOUT/CLKOUT Outputs. Outputs are<br>enabled when HIGH or when left open; OE pin has internal pullup resistor. Disables<br>both outputs when LOW. CLKOUT goes LOW, CLKOUT goes HIGH. |

| 14                | S0              | Tri-Level Input           | Multiplier Select Pin; When Left Open, Defaults to V_DD $\div$ 2                                                                                                                                            |

| 16                | X2              | Crystal Input             | Crystal Input                                                                                                                                                                                               |

\*The PECL Outputs are 15 mA open collector and must be DC loaded and AC terminated. See Figures 4, 5 and 6.

#### Table 4. ATTRIBUTES

| Characteristics                                                          | Value                       |  |  |  |

|--------------------------------------------------------------------------|-----------------------------|--|--|--|

| ESD Protection Human Body Model<br>Machine Model<br>Charged Device Model | > 1 kV<br>> 150 V<br>> 1 kV |  |  |  |

| Moisture Sensitivity, Indefinite Time Out of Drypack (Note 1)            | Level 1                     |  |  |  |

| Flammability Rating Oxygen Index: 28 to 34                               | UL 94 V-0 @ 0.125 in        |  |  |  |

| Transistor Count                                                         | 1145 Devices                |  |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test                   |                             |  |  |  |

1. For additional information, see Application Note AND8003/D.

## Table 5. MAXIMUM RATINGS

| Symbol          | Parameter                   | Condition 1 | Condition 2 | Rating                             | Unit |

|-----------------|-----------------------------|-------------|-------------|------------------------------------|------|

| V <sub>CC</sub> | Positive Power Supply       | GND = 0 V   |             | 6                                  | V    |

| VI              | Input Voltage               |             |             | $GND-0.5 \leq V_I \leq V_{DD}+0.5$ | V    |

| T <sub>A</sub>  | Operating Temperature Range |             |             |                                    |      |

GND

## **APPLICATIONS INFORMATION**

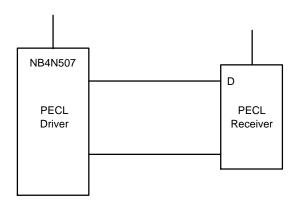

High Frequency Differential PECL Oscillators: The NB4N507A, along with a low frequency fundamental mode crystal, can build a high frequency differential PECL output oscillator. For example, a 10 MHz crystal connected to the NB4N507A with the 12X output selected (S1 = 0, S0 = 1) produces a 120 MHz PECL output clock.

#### **Crystal Oscillator Input Interface**

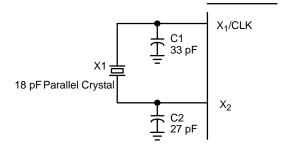

The NB4N507A features an integrated crystal oscillator to minimize system implementation costs. The oscillator circuit is a parallel resonant circuit and thus, for optimum performance, a parallel resonant crystal should be used.

As the oscillator is somewhat sensitive to loading on its inputs, the user is advised to mount the crystal as close to the NB4N507A as possible to avoid any board level parasitics. Surface mount crystals are recommended, but not required.

Figure 7. Crystal Input Interface

**High Frequency VCXO:** The bandwidth of the PLL is guaranteed to be greater than 10 kHz. This means that the PLL will track any modulation on the input with a frequency of less than 10 kHz. By using this property, a low frequency VCXO can be built. The output can then be multiplied by the NB4N507A, thereby producing a high frequency VCXO.

**High Frequency TCXO:** Extending the previous application, an inexpensive, low frequency TCXO can be built and the output frequency can be multiplied using the NB4N507A.

## **Resource Reference of Application Notes**

| AN1405/D  | - | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | - | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | - | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | - | Metastability and the ECLinPS Family        |

| AN1568/D  | - | Interfacing Between LVDS and ECL            |

| AN1672/D  | - | The ECL Translator Guide                    |

| AND8001/D | - | Odd Number Counters Design                  |

| AND8002/D | - | Marking and Date Codes                      |

| AND8020/D | - | Termination of ECL Logic Devices            |

| AND8066/D | - | Interfacing with ECLinPS                    |

| AND8090/D | - | AC Characteristics of ECL Devices           |

|           |   |                                             |

SOIC-16 9.90x3.90x1.50 1.27P CASE 751B ISSUE L

#### SOIC-16 9.90x3.90x1.50 1.27P CASE 751B ISSUE L

#### GENERIC MARKING DIAGRAM\*

| 16 | H | H   | A   | H.  | H.  | -A  | A   | E  |

|----|---|-----|-----|-----|-----|-----|-----|----|

|    |   | XXX | XX) | XX) | XX) | XX) | XX  | G  |

|    |   | XX  | XX  | XX  | XX  | XX  | XX) | хI |

|    | 0 |     | A   | WĽ  | YW  | /W  |     |    |

| 1  | Έ | H   | Н   | Н   | Н   | Н   | Н   | Ъ  |

XXXXX = Specific Device Code

A = Assembly Location

- WL = Wafer Lot

- Y = Year

- WW = Work Week

- G = Pb–Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| S, | 1:<br>2. BAS<br>3.<br>4. C C<br>5.<br>6. BAS<br>7. C C<br>9. BAS<br>10.<br>11. C C<br>13. BAS<br>14. C C<br>15.<br>16. C C                                                                                                                                                         | S 2:<br>1. CA<br>2. A<br>3. C<br>4. CA<br>5. CA<br>6. C<br>7. A<br>8. CA<br>9. CA<br>10. A<br>11. C<br>12. CA<br>13. CA<br>13. CA<br>14. C<br>15. A<br>16. CA | s<br>C<br>C<br>C | 3: $S$<br>1. C C , #1<br>2. BAS, #1<br>3. , #1<br>4. C C , #1<br>5. C C , #2<br>6. BAS, #2<br>7. , #2<br>8. C C , #2<br>9. C C , #3<br>10. BAS, #3<br>11. , #3<br>12. C C , #4<br>14. BAS, #4<br>15. , 44<br>15. , 44 | 4:<br>1. C C , #1<br>2. C C , #2<br>4. C C , #2<br>5. C C , #3<br>6. C C , #3<br>7. C C , #4<br>8. C C , #4<br>9. BAS , #4<br>10. , #4<br>11. BAS , #3<br>12. , #3<br>13. BAS , #2<br>14. , #2<br>15. BAS , #1<br>16. , #1 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S  | 5:<br>A, #1<br>2.<br>A, #1<br>3.<br>A, #2<br>4.<br>A, #2<br>5.<br>A, #3<br>6.<br>A, #3<br>6.<br>A, #4<br>9.<br>A, #4<br>9.<br>A, #4<br>10.<br>S, C, #4<br>11.<br>A, #3<br>12.<br>S, C, #3<br>13.<br>A, #1<br>14.<br>S, C, #2<br>15.<br>A, #1<br>16.<br>S, C, #1<br>16.<br>S, C, #1 | S 6:<br>1. CA<br>2. CA<br>3. CA<br>4. CA<br>5. CA<br>6. CA<br>7. CA<br>8. CA<br>9. A<br>10. A<br>11. A<br>12. A<br>13. A<br>14. A<br>15. A<br>16. A           | S.               | 7:                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |

| DOCUMENT NUMBER: | 98ASB42566B Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.50 1                                                                                                                                                                     | PAGE 2 OF 2 |  |  |  |

|                  |                                                                                                                                                                                              |             |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi