# **5 V ECL 1:4 Clock Distribution Chip**

## MC10EL15, MC100EL15

#### Description

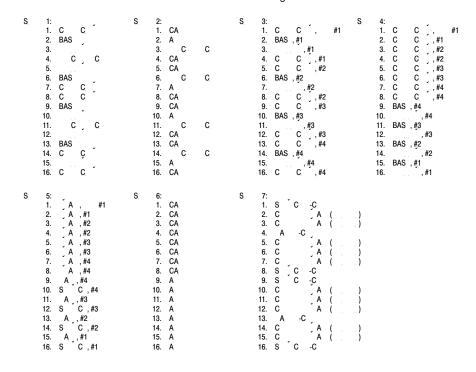

The MC10EL/100EL15 is a low skew 1:4 clock distribution chip designed explicitly for low skew clock distribution applications. The  $V_{BB}$  pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to  $V_{BB}$  as a switching reference voltage.  $V_{BB}$  may also rebias AC coupled inputs. When used, decouple  $V_{BB}$  and  $V_{CC}$  via a 0.01  $\mu F$  capacitor and limit current sourcing or sinking to 0.5 mA. When not used,  $V_{BB}$  should be left open.

The EL15 features a multiplexed clock input to allow for the distribution of a lower speed scan or test clock along with the high speed system clock. When LOW (or left open and pulled LOW by the input pulldown resistor) the SEL pin will select the differential clock input.

The common enable  $(\overline{EN})$  is synchronous so that the outputs will only be enabled/disabled when they are already in the LOW state. This avoids any chance of generating a runt clock pulse when the device is

<del>1</del>

Figure 1. Logic Diagram and Pinout Assignment

#### **Table 4. MAXIMUM RATINGS**

| Symbol           | Parameter                                          | Condition 1                                    | Condition 2                                                       | Rating    | Unit |

|------------------|----------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------|-----------|------|

| V <sub>CC</sub>  | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                                                   | 8         | V    |

| V <sub>EE</sub>  | NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V                          |                                                                   | -8        | V    |

| l <sub>out</sub> | Output Current                                     | Continuous<br>Surge                            |                                                                   | 50<br>100 | mA   |

| VI               | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{c} V_I \leq V_{CC} \\ V_I \geq V_{EE} \end{array}$ | 6<br>-6   |      |

#### Table 8. 100EL SERIES NECL DC CHARACTERISTICS ( $V_{CC} = 0 \text{ V}$ ; $V_{EE} = -5.0 \text{ V}$ (Note 1))

|                 | ( 00 / 22                    |       |            |       |       |       |      |       |      |      |      |

|-----------------|------------------------------|-------|------------|-------|-------|-------|------|-------|------|------|------|

|                 |                              |       | -40°C 25°C |       | 85°C  |       |      |       |      |      |      |

| Symbol          | Characteristic               | Min   | Тур        | Max   | Min   | Тур   | Max  | Min   | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current         |       | 25         | 35    |       | 25    | 35   |       | 25   | 38   | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2) | -1085 | -1005      | -880  | -1025 | -955  | -880 | -1025 | -955 | -880 | mV   |

| $V_{OL}$        | Output LOW Voltage (Note 2)  | -1830 | -1695      | -1555 | -1810 | -1705 |      |       |      |      |      |

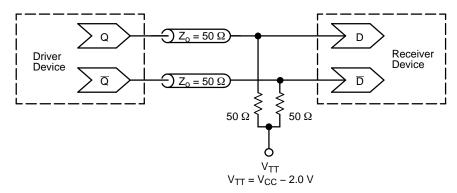

Figure 2. Typical Termination for Output Driver and Device Evaluation (See Application Note <u>AND8020/D</u> – Termination of ECL Logic Devices.)

#### **Resource Reference of Application Notes**

AN1405/D – ECL Clock Distribution Techniques

AN1406/D – Designing with PECL (ECL at +5.0 V)

AN1503/D – ECLinPS™ I/O SPiCE Modeling Kit

AN1504/D – Metastability and the ECLinPS Family

AN1568/D – Interfacing Between LVDS and ECL

AN1672/D - The ECL Translator Guide

VD91347tability 7.9228 4.92 3-5Odd5T4 1 Tf7.9228 4.913452/D

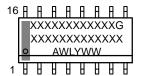

#### SOIC-16 9.90x3.90x1.50 1.27P CASE 751B ISSUE L

## **SOIC-16 9.90x3.90x1.50 1.27P**CASE 751B ISSUE L

**DATE 29 MAY 2024**

## GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

A = Assembly Location

WL = Wafer Lot

Y = Year

WW = Work Week

G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42566B                    | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |

|------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| DESCRIPTION:     | : SOIC-16 9.90X3.90X1.50 1.27P |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.