# 3.3 V ECL ÷4 Divider

#### Description

The MC100LVEL33 is an integrated ÷4 divider. The LVEL is functionally equivalent to the EL33 and works from a 3.3 V supply.

The reset pin is asynchronous and is asserted on the rising edge. Upon power-up, the internal flip-flops will attain a random state; the reset allows for the synchronization of multiple LVEL33's in a system.

The  $V_{BB}$  pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to  $V_{BB}$  as a switching reference voltage.  $V_{BB}$  may also rebias AC coupled inputs. When used, decouple  $V_{BB}$  and V

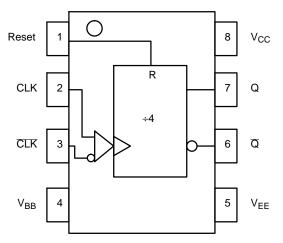

Figure 1. Logic Diagram and Pinout Assignment

#### **Table 1. PIN DESCRIPTION**

| PIN             | FUNCTION                         |

|-----------------|----------------------------------|

| CLK*, CLK**     | ECL Differential Clock Inputs    |

| Q, Q            | ECL Differential Data ÷4 Outputs |

| Reset*          | ECL Asynch Reset                 |

| $V_{BB}$        | Reference Voltage Output         |

| V <sub>CC</sub> | Positive Supply                  |

| V <sub>EE</sub> | Negative Supply                  |

| 1               |                                  |

<sup>\*</sup> Pins will default LOW when open due to internal 75  $k\Omega$  resistor to  $V_{\mbox{\footnotesize{EE}}}$

#### **Table 2. MAXIMUM RATINGS**

| Symbol           | Parameter                                          | Condition 1                                    | Condition 2                                                       | Rating            | Unit |

|------------------|----------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------|-------------------|------|

| V <sub>CC</sub>  | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                                                   | 8 to 0            | V    |

| V <sub>EE</sub>  | NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V                          |                                                                   | -8 to 0           | V    |

| V <sub>I</sub>   | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{c} V_I \leq V_{CC} \\ V_I \geq V_{EE} \end{array}$ | 6 to 0<br>-6 to 0 | V    |

| I <sub>out</sub> | Output Current                                     | Continuous<br>Surge                            |                                                                   | 50<br>100         | mA   |

| $I_{BB}$         | V <sub>BB</sub> Sink/Source                        |                                                |                                                                   | ± 0.5             | mA   |

| T <sub>A</sub>   | Operating Temperature Range                        |                                                |                                                                   | -40 to +85        | °C   |

| T <sub>stg</sub> | Storage Temperature Range                          |                                                |                                                                   | -65 to +150       | °C   |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | SOIC                                                              |                   |      |

<sup>\*\*</sup> Pins will default to 1/2 V\_{CC} when open due to internal resistors: 75 k $\Omega$  to V\_{EE} and 75 k $\Omega$  to V\_{CC}

### Table 3. LVPECL DC CHARACTERISTICS ( $V_{CC} = 3.3 \text{ V}; V_{EE} = 0.0 \text{ V} \text{ (Note 1))}$

|                 |                              | -40°C |      | 25°C |      |            | 85°C |      |      |          |      |

|-----------------|------------------------------|-------|------|------|------|------------|------|------|------|----------|------|

| Symbol          | Characteristic               | Min   | Тур  | Max  | Min  | Тур        | Max  | Min  | Тур  | Max      | Unit |

| I <sub>EE</sub> | Power Supply Current         |       | 33   | 37   |      | 33         | 37   |      | 35   | 39       | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2) | 2215  | 2295 | 2420 | 2275 | 2345       | 2420 | 2275 | 2345 | 2420     | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)- | 1470  | 1605 | 1745 |      | <u>-</u> ' | •    | •    | •    | <u>.</u> | -    |

$\textbf{Table 5. AC CHARACTERISTICS} \ (\text{V}_{CC} = 3.3 \ \text{V}; \ \text{V}_{EE} = 0.0 \ \text{V} \ \text{or} \ \text{V}_{CC} = 0.0 \ \text{V}; \ \text{V}_{EE} = -3.3 \ \text{V} \ (\text{Note 1}))$

|                                      |                                                            | -40°C      |     | 25°C |     |     | 85°C |     |     |     |      |

|--------------------------------------|------------------------------------------------------------|------------|-----|------|-----|-----|------|-----|-----|-----|------|

| Symbol                               | Characteristic                                             | Min        | Тур | Max  | Min | Тур | Max  | Min | Тур | Max | Unit |

| f <sub>max</sub>                     | Maximum Toggle Frequency                                   | 3.4        |     |      | 3.8 | 4.0 |      | 3.8 |     |     | GHz  |

| <sup>†</sup> PLH<br><sup>†</sup> PHL | Propagation Delay CLK to Q (Diff) CLK to Q (SE) Reset to Q | 530<br>530 | -   | -    | -   | -   | -    |     | -   | -   | -    |

Figure 2. Typical Termination for Output Driver and Device Evaluation (See Application Note  $\underline{\text{AND8020/D}}$  – Termination of ECL Logic Devices)

#### TSSOP 8 CASE 948R-02 ISSUE A

### **DATE 04/07/2000**

|     | MILLIMETERS |     | INC | HES |  |

|-----|-------------|-----|-----|-----|--|

| DIM | MIN         | MAX | MIN | MAX |  |

| Α   |             |     |     |     |  |

|     |             |     |     |     |  |

|     |             |     |     |     |  |

|     |             |     |     |     |  |

|     |             |     |     |     |  |

|     |             |     |     |     |  |

|     |             |     |     |     |  |

|     |             |     |     |     |  |