# onsemi

## **3.3 V ECL 8-Bit Synchronous Binary Up Counter**

# MC100EP016A

#### Description

The MC100EP016A is a high-speed synchronous, presettable, cascadeable 8-bit binary counter. Architecture and operation are the same as the ECLinPS family MC100E016 with higher operating speed.

The counter features internal feedback to  $\overline{\text{TC}}$  gated by the TCLD (Terminal Count Load) pin. When TCLD is LOW (or left open, in which case it is pulled LOW by the internal pulldowns), the  $\overline{\text{TC}}$  feedback is disabled, and counting proceeds continuously, with  $\overline{\text{TC}}$  going LOW to indicate an all-one state. When TCLD is HIGH, the TC feedback causes the counter to automatically reload upon TC = LOW, thus functioning as a programmable counter. The Qn outputs do not need to be terminated for the count function to operate properly. To

minimize noise and power, unused Q outputs 6.2res integ mA5T10 0 017.3( Q)1TT5 1 Tf13.020. -.0021 Tc(For additional environment of the context of the contex

Warning: All  $V_{CC}$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

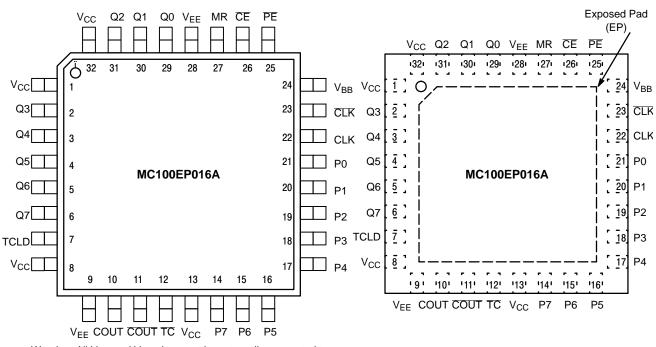

Figure 1. 32-Lead LQFP Pinout (Top View)

Figure 2. 32-Lead QFN Pinout (Top View)

#### Table 1. PIN DESCRIPTION

Pin

CL(Data OutputsC)Tj ET 179032 7-39417.9019 15.307 N DES532.189 7-39417.9019 15.307 N DE 179032 388347537-3.76(3.36645 ref BT 8 0 0 8694.36)3.9109 Tm 0 Tc

#### Table 4. ATTRIBUTES

| Characteristics                                               |                                                           |  |

|---------------------------------------------------------------|-----------------------------------------------------------|--|

| Internal Input Pulldown Resistor                              |                                                           |  |

| Internal Input Pullup Resistor                                |                                                           |  |

| ESD Protection                                                | Human Body Model<br>Machine Model<br>Charged Device Model |  |

| Moisture Sensitivity, Indefinite Time Out of Drypack (Note 1) |                                                           |  |

|                                                               | LQFP-32<br>QFN-32                                         |  |

| Flammability Rating Oxygen Index: 28 to 34                    |                                                           |  |

| Transistor Count                                              |                                                           |  |

| Meets or exceeds JEDEC Spec El                                | A/JESD78 IC Latchup Test                                  |  |

1. For additional information, see Application Note AND8003/D.

#### Table 5. MAXIMUM RATINGS

| Symbol           | Parameter                                          | Condition 1                                    |                  |  |

|------------------|----------------------------------------------------|------------------------------------------------|------------------|--|

| V <sub>CC</sub>  | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                  |  |

| V <sub>EE</sub>  | NECL Mode Power Supply                             | $V_{CC} = 0 V$                                 |                  |  |

| VI               | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | V <sub>I</sub> : |  |

| l <sub>out</sub> | Output Current                                     | Continuous<br>Surge                            |                  |  |

| I <sub>BB</sub>  | V <sub>BB</sub> Sink/Source                        |                                                |                  |  |

| T <sub>A</sub>   | Operating Temperature Range                        |                                                |                  |  |

| T <sub>stg</sub> | Storage Temperature Range                          |                                                |                  |  |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)<br>QFN    | <b>0 lfpm</b> 500 lfpm32<br>500 lfpm           | 32<br>32         |  |

| Table 8. | AC CHARACTERISTICS V <sub>EE</sub> = -3.0 V to - | -Î | 8.6 V; V <sub>CC =</sub> 0 V or \ | (cc | $_{\rm C} = 3.0$ V to 3.6 V | $V_{EE} = 0$ | ) V (Note 8) |

|----------|--------------------------------------------------|----|-----------------------------------|-----|-----------------------------|--------------|--------------|

|          |                                                  |    |                                   |     |                             |              |              |

|        |                                                                 |     | -40°C |     | 25°C |     |     | 70°C |     |     |      |

|--------|-----------------------------------------------------------------|-----|-------|-----|------|-----|-----|------|-----|-----|------|

| Symbol | Characteristic                                                  | Min | Тур   | Max | Mir  | Тур | Мах | Min  | Тур | Max | Unit |

| fcount | Maximum Frequency<br>Count & Division Modes<br>Q, TC, COUT/COUT | 1.3 | 1.5   |     | 1.2  | 1.4 |     |      |     |     |      |

#### **APPLICATIONS INFORMATION**

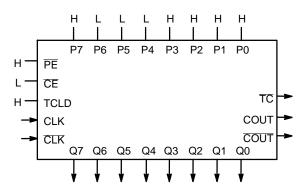

**Cascading Multiple EP016A Devices** For applications which call for larger than 8-bit counters

#### **APPLICATIONS INFORMATION** (continued)

Figure 5. Mod 2 to 256 Programmable Divider

To determine what value to load into the device to accomplish the desired division, the designer simply subtracts the binary equivalent of the desired divide ratio from the binary value for 256. As an example for a divide ratio of 113:

Pn's =  $256 - 113 = 8F_{16} = 1000 1111$  where:

P0 = LSB and P7 = MSB

Forcing this input condition as per the setup in Figure 5 will result in the waveforms of Figure 6. Note that the  $\overline{\text{TC}}$  output is used as the divide output and the pulse duration is equal to a full clock period. For even divide ratios, twice the desired divide ratio can be loaded into the EP016A and the  $\overline{\text{TC}}$  output can feed the clock input of a toggle flip flop to aivius 1 0 0 RCLK0 0 2 TD2divTD-338 7.80R

#### **APPLICATIONS INFORMATION** (continued)

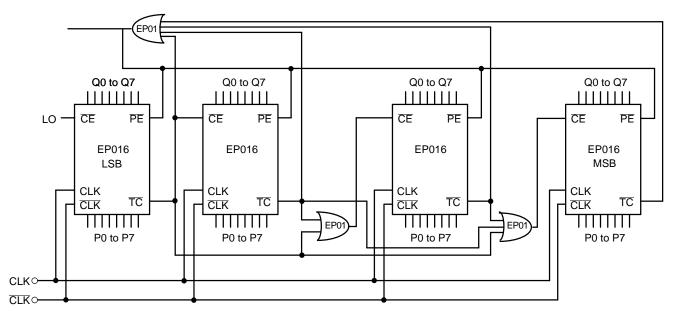

Figure 7. 32-Bit Cascaded EP016A Programmable Divider

Figure 7 shows a typical block diagram of a 32-bit divider chain. Once again to maximize the frequency of operation EP01 OR gates were used. For lower frequency applications a slower OR gate could replace the EP01. Note that for a 16-bit divider the OR function feeding the  $\overline{PE}$  (program enable) input CANNOT be replaced by a wire OR tie as the  $\overline{TC}$  output of the least significant EP016A must also feed the  $\overline{CE}$  input of the most significant EP016A. If the two  $\overline{TC}$ outputs were OR tied the cascaded count operation would not operate properly. Because in the cascaded form the  $\overline{PE}$ feedback is external and requires external gating, the maximum frequency of operation will be significantly less than the same operation in a single device.

#### **ORDERING INFORMATION**

| Device           | Package              | Shipping <sup>†</sup> |

|------------------|----------------------|-----------------------|

| MC100EP016AFAG   | LQFP-32<br>(Pb-Free) | 250 Units / Tray      |

| MC100EP016AMNG   | QFN-32<br>(Pb-Free)  | 74 Units / Rail       |

| MC100EP016AMNR4G | QFN-32<br>(Pb-Free)  | 1000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **Resource Reference of Application Notes**

| AN1405/D  | _ | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | _ | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | _ | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | _ | Metastability and the ECLinPS Family        |

| AN1568/D  | _ | Interfacing Between LVDS and ECL            |

| AN1672/D  | _ | The ECL Translator Guide                    |

| AND8001/D | _ | Odd Number Counters Design                  |

| AND8002/D | _ | Marking and Date Codes                      |

| AND8020/D | _ | Termination of ECL Logic Devices            |

| AND8066/D | _ | Interfacing with ECLinPS                    |

| AND8090/D | _ | AC Characteristics of ECL Devices           |

ECLinPS is a trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

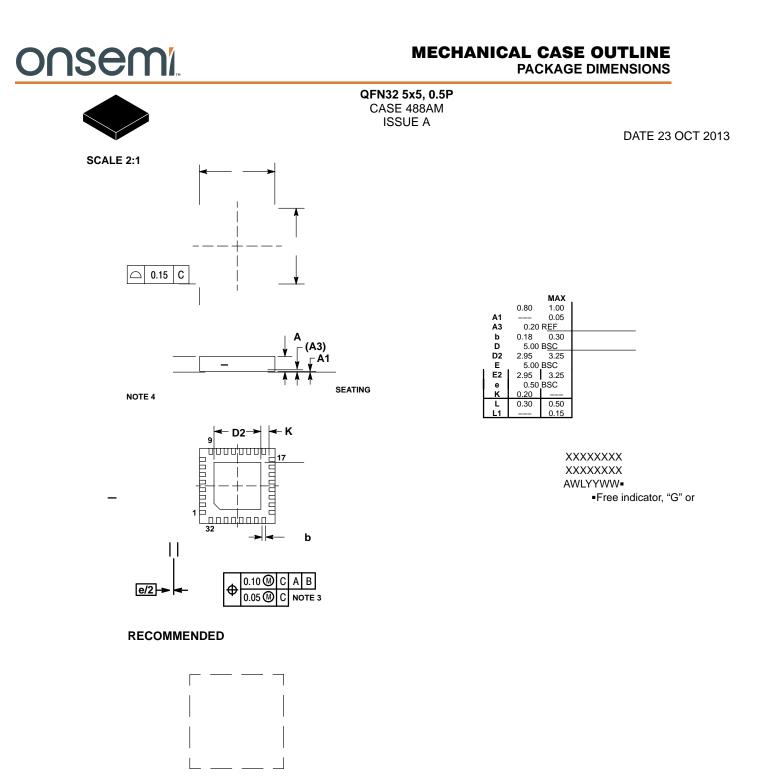

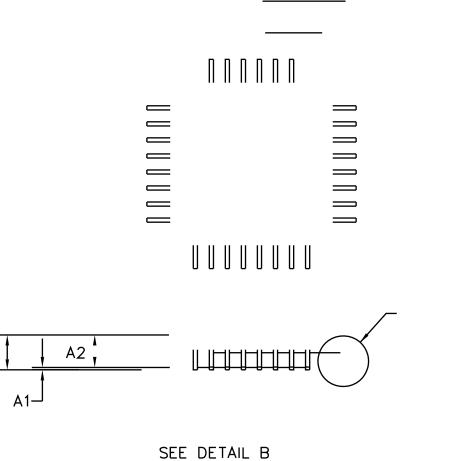

| | PITCH

DIMENSION: MILLIMETERS

| DOCUMENT NUMBER: | 98AON20032D |  |

|------------------|-------------|--|

|                  |             |  |

1, 1,40 1,45 0,30 0,45

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi