# Onsemi

# **AC/DC** to Logic **Interface Optocoupler**

# **HCPL3700M**

#### Description

The HCPL3700M voltage/current threshold detection optocoupler consists of an AIGaAs LED connected to a threshold sensing input buffer IC which are optically coupled to a high gain darlington output. The input buffer chip is capable of controlling threshold levels over a wide range of input voltages with a single resistor. The output is TTL and CMOS compatible.

#### Features

AC or DC Input Programmable Sense Voltage Logic Level Compatibility Threshold Guaranteed Over Temperature (0°C to 70°C) Safety and Regulatory Approvals ◆ UL1577, 5,000 VAC<sub>RMS</sub> for 1 Minute

◆ DIN EN/IEC60747-5-5

These are Pb-Free Devices

#### Applications

Low Voltage Detection 5 V to 240 V AC/DC Voltage Sensing Relay Contact Monitor Current Sensing Microprocessor Interface Industrial Controls

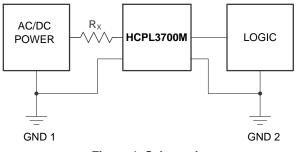

Figure 1. Schematic

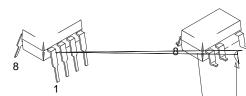

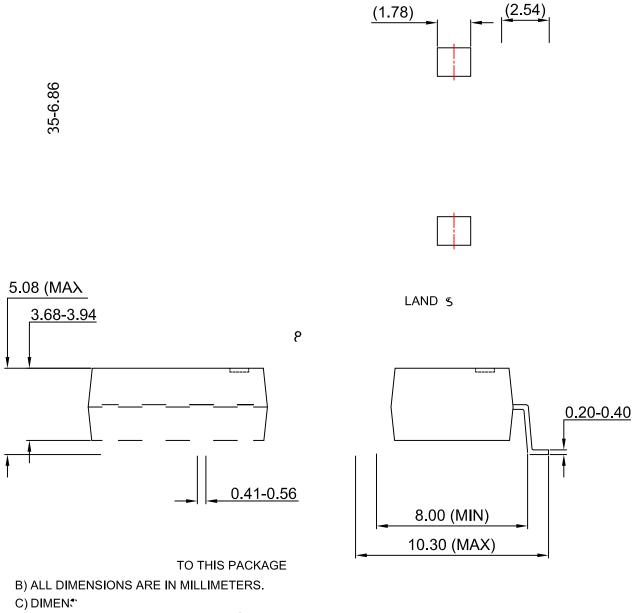

PDIP8 9.655x6.6, 2.54P CASE 646CQ

PDIP8 GW CASE 709AC

#### MARKING DIAGRAM

= Assembly Package Code

V

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 10 of this data sheet.

**SAFETY AND INSULATION RATINGS** (As per DIN EN/IEC 60747–5–5, this optocoupler is suitable for "safe electrical insulation" only within the safety limit data. Compliance with the safety ratings shall be ensured by means of protective circuits.)

| Parameter                                                                           |        | Characteristics |

|-------------------------------------------------------------------------------------|--------|-----------------|

| Installation Classifications per DIN VDE 0110/1.89 Table 1, For Rated Mains Voltage | <150 V |                 |

| Symbol     Parameter     Test Conditions | Min. Typ. |

|------------------------------------------|-----------|

|------------------------------------------|-----------|

| Symbol             | Parameter                                                | Test Conditions                                                                                                                       | Min. | Тур. | Max. | Units |

|--------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

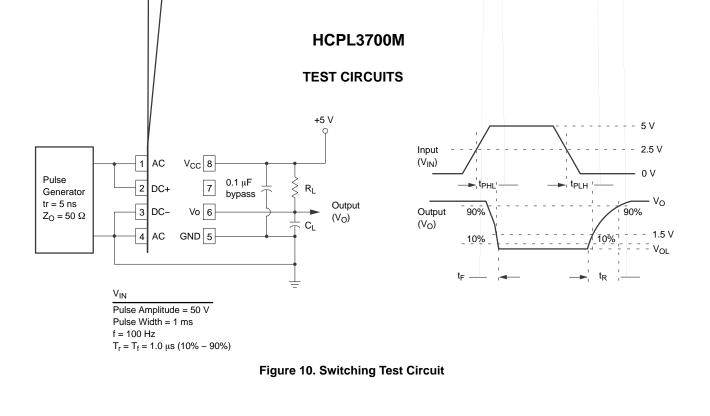

| t <sub>PHL</sub>   | Propagation Delay Time<br>(to Output Low Level)          | $R_L = 4.7 \text{ k}\Omega, C_L = 30 \text{ pF} (\text{Note 7})$                                                                      |      | 6.0  | 15   | μS    |

| t <sub>PLH</sub>   | Propagation Delay Time<br>(to Output High Level)         | $R_L$ = 4.7 kΩ, $C_L$ = 30 pF (Note 7)                                                                                                |      | 25.0 | 40   | μS    |

| t <sub>R</sub>     | Output Rise Time (10%–90%)                               | $R_L = 4.7 \text{ k}\Omega, C_L = 30 \text{ pF}$                                                                                      |      | 45   |      | μs    |

| t <sub>F</sub>     | Output Fall Time (90%–10%)                               | $R_L = 4.7 \text{ k}\Omega, C_L = 30 \text{ pF}$                                                                                      |      | 0.5  |      | μs    |

| ICM <sub>H</sub> I | Common Mode Transient<br>Immunity (at Output High Level) | $    I_{IN} = 0 \text{ mA}, R_L = 4.7 \text{ k}\Omega, \\ V_{Omin} = 2.0 \text{ V}, V_{CM} = 1400 \text{ V} \text{ (Notes 8, 9)} $    |      | 4000 |      | V/μs  |

| ICMLI              | Common Mode Transient<br>Immunity (at Output Low Level)  | $    I_{IN} = 3.11 \text{ mA}, R_L = 4.7 \text{ k}\Omega, \\ V_{Omax} = 0.8 \text{ V}, V_{CM} = 1400 \text{ V} \text{ (Notes 8, 9)} $ |      | 600  |      | V/μs  |

#### SWITCHING CHARACTERISTICS ( $T_A = 25^{\circ}C$ , $V_{CC} = 5$ V unless otherwise specified)

#### ISOLATION CHARACTERISTICS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol           | Parameter                     | Test Conditions                                                                  | Min.  | Тур.             | Max. | Units              |

|------------------|-------------------------------|----------------------------------------------------------------------------------|-------|------------------|------|--------------------|

| V <sub>ISO</sub> | Withstand Isolation Voltage   | RH $\leq$ 50%, I <sub>I-O</sub> $\leq$ 10 µA, t = 1 min, f = 50 Hz (Note 10, 11) | 5,000 | -                | -    | VAC <sub>RMS</sub> |

| R <sub>I-O</sub> | Resistance (Input to Output)  | V <sub>IO</sub> = 500 V <sub>DC</sub> (Note 10)                                  | -     | 10 <sup>12</sup> | -    | Ω                  |

| C <sub>I–O</sub> | Capacitance (Input to Output) | $f = 1 \text{ MHz}, \text{ V}_{\text{IO}} = 0 \text{ V}_{\text{DC}}$             | -     | 0.6              | -    | pF                 |

7. T<sub>PHL</sub> propagation delay is measured from the 2.5 V level of the leading edge of a 5.0 V input pulse (1 µs rise time) to the 1.5 V level on the Is the result of the output pulse. T<sub>PLH</sub> propagation delay is measured on the trailing edges of the input and output pulse. (Refer to Fig. 10)

Common mode transient immunity in logic high level is the maximum tolerable (positive) dV<sub>cm</sub>/dt on the leading edge of the common mode

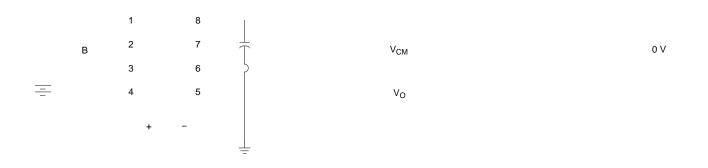

Common mode transient immunity in logic high level is the maximum tolerable (positive) dV<sub>cm</sub>/dt on the leading edge of the common mode pulse signal V<sub>CM</sub>, to assure that the output will remain in a logic high state (i.e., V<sub>O</sub> > 2.0 V). Common mode transient immunity in logic low level is the maximum tolerable (negative) dV<sub>cm</sub>/dt on the trailing edge of the common mode pulse signal, V<sub>CM</sub>, to assure that the output will remain in a logic low state (i.e., V<sub>O</sub> < 0.8 V). Refer to Fig. 11.</li>

In applications where dV<sub>cm</sub>/dt may exceed 50,000 V/µs (Such as static discharge), a series resistor, R<sub>CC</sub>, should be included to protect the detector chip from destructive surge currents. The recommended value for R<sub>CC</sub> is 240 V per volt of allowable drop in V<sub>CC</sub>

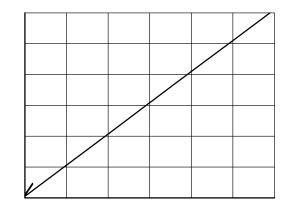

## **TYPICAL PERFORMANCE CURVES**

I<sub>IN</sub>, INPUT CURRENT (mA)

T<sub>A</sub>, TEMPERATURE (°C)

# TYPICAL PERFORMANCE CURVES (continued)

Figure 11. Test Circuit for Common Mode Transient Immunity and Typical Waveforms

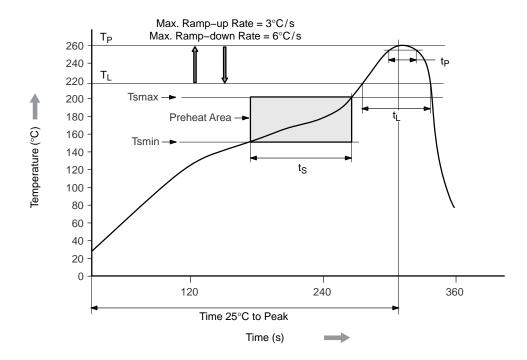

#### **REFLOW PROFILE**

| Profile Freature                                          | Pb-Free Assembly Profile |  |  |

|-----------------------------------------------------------|--------------------------|--|--|

| Temperature Minimum (Tsmin)                               | 150°C                    |  |  |

| Temperature Maximum (Tsmax)                               | 200°C                    |  |  |

| Time (t <sub>S</sub> ) from (Tsmin to Tsmax)              | 60 to 120 s              |  |  |

| Ramp-up Rate (t <sub>L</sub> to t <sub>P</sub> )          | 3°C/s maximum            |  |  |

| Liquidous Temperature (T <sub>L</sub> )                   | 217°C                    |  |  |

| Time (t <sub>L</sub> ) Maintained Above (T <sub>L</sub> ) | 60 to 150 s              |  |  |

| Peak Body Package Temperature                             | 260°C +0°C/–5°C          |  |  |

| Time (t <sub>P</sub> ) within 5°C of 260°C                | 30 s                     |  |  |

| Ramp–down Rate (T <sub>P</sub> to T <sub>L</sub> )        | 6°C/s maximum            |  |  |

| Time 25°C to Peak Temperature                             | 8 minutes maximum        |  |  |

Figure 12. Reflow Profile

#### ORDERING INFORMATION

| Part Number | Package   | Packing Method <sup>†</sup> |

|-------------|-----------|-----------------------------|

| HCPL3700M   | DIP 8–Pin | 50 Units / Tube             |

| HCPL3700SM  |           |                             |

PDIP8 9.655 x6.6, 2.54P CASE 646CQ ISSUE O

DATE 18 SEP 2017

⊂ E ⊃N₊ AND TIE BAR EXTRUSI

DATE 31 JUL 2016

**EAR EXTRUSI**

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi