# onsemi

# F II Config rable 8-Bi I<sup>2</sup>C-Con rolled GPIO E pander

# FXL6408

#### Description

The FXL6408 is an 8-bit I<sup>2</sup>C-controlled GPIO expander. When configured in Input Mode, the FXL6408 monitors the input ports for data transitions and signals the baseband by asserting the  $\overline{INT}$  pin. The input default values can be programmed independently, allowing customized input detection. All inputs can be configured with pull-up or pull-down resistors to pre-

## **PIN CONFIGURATION**

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Symbol             | Parameter                                           | Condition                         | Min  | Max  | Unit |

|--------------------|-----------------------------------------------------|-----------------------------------|------|------|------|

| $V_{CC}, V_{DDIO}$ | Supply Voltages                                     |                                   | -0.5 | 4.6  | V    |

| V <sub>IN</sub>    | DC Input Voltage                                    |                                   | -0.5 | 4.0  | V    |

| V <sub>OUT</sub>   | Output Voltage (Note 1)                             |                                   | -0.5 | 4.0  | V    |

| Ι <sub>ΙΚ</sub>    | DC Input Diode Current                              | V <sub>IN</sub> < 0 V             |      | -50  | mA   |

| I <sub>OK</sub>    | DC Output Diode Current                             | V <sub>OUT</sub> < 0 V            |      | -50  | mA   |

| I <sub>OL</sub>    | DC Output Sink Current                              |                                   |      | +50  | mA   |

| I <sub>CC</sub>    | DC V <sub>CC</sub> or Ground Current per Supply Pin |                                   |      | ±100 | mA   |

| T <sub>STG</sub>   | Storage Temperature Range                           |                                   | -65  | +150 | °C   |

| TJ                 | Junction Temperature under Bias                     |                                   |      | +150 | °C   |

| ΤL                 | Junction Lead Temperature, Soldering 10 seconds     |                                   |      | +260 | °C   |

| $\theta_{JA}$      | Thermal Resistance, Junction-to-Ambient             |                                   |      | 115  | °C/W |

| ESD                | Electrostatic Discharge Capability                  | Human Body Model, JESD22-A114     |      | 4    | kV   |

|                    |                                                     | Charged Device Model, JESD22-C101 |      | 2    |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All output current absolute maximum ratings must be observed.

#### Table 3. RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                             | Condition                                                 | Min  | Max               | Unit |

|---------------------------------|---------------------------------------|-----------------------------------------------------------|------|-------------------|------|

| V <sub>CC</sub>                 | Supply Voltage Operating              |                                                           | 1.65 | 3.60              | V    |

| V <sub>DDIO</sub>               | I/O Side Reference Voltage            |                                                           | 1.65 | 4.00              | V    |

| V <sub>IN</sub>                 | Input Voltage on I/O Pins             |                                                           | 0    | 4.00              | V    |

| V <sub>OUT</sub>                | Output Voltage                        |                                                           | 0    | V <sub>DDIO</sub> | V    |

| T <sub>A</sub>                  | Operating Temperature                 |                                                           | -40  | +85               | °C   |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Times to I/O Pins | $V_{\mbox{\scriptsize DDIO}}$ at 1.8 V, 2.5 V $\pm 0.2$ V | 0    | 200               | ns/V |

|                                 |                                       |                                                           |      |                   |      |

#### Table 4. DC ELECTRICAL CHARACTERISTICS

|                  |                               |                                |                     | T <sub>A</sub> = 25°C |     | T <sub>A</sub> = −40 to<br>85°C |     |      |      |

|------------------|-------------------------------|--------------------------------|---------------------|-----------------------|-----|---------------------------------|-----|------|------|

| Symbol           | Parameter                     | Condition                      | V <sub>CC</sub> (V) | Min                   | Тур | Max                             | Min | Max  | Unit |

| RST, ADDI        | RST, ADDR, SDA, SCL, INT Pins |                                |                     |                       |     |                                 |     |      |      |

| V <sub>POR</sub> | Power-On Reset Voltage        | $V_{DDIO} = 0$ to 4.0 V        |                     |                       |     | 1.25                            |     | 1.25 | V    |

| I <sub>IN</sub>  | Input Leakage Current         | $0 \leq V_{IN} \leq V_{CCCC0}$ | -                   | -                     |     | -                               |     | -    |      |

|                         |                                                                                                  | Fast | Fast Mode |      |

|-------------------------|--------------------------------------------------------------------------------------------------|------|-----------|------|

| Symbol                  | Parameter                                                                                        | Min  | Max       | Unit |

| t <sub>W</sub>          | Reset Pulse Duration (see Figure 3)                                                              | 150  |           | ns   |

| t <sub>RST_GLITCH</sub> | Input Glitch Rejection on RST Pin (see Figure 3)                                                 | 50   | 150       | ns   |

| t <sub>RESET</sub>      | Reset Time, Total Time from Rising Edge of Reset Pulse to Falling Edge of INT Pin (see Figure 4) |      | 150       | ns   |

| t <sub>IV</sub>         | Time from Input Default State Change to INT Pin Driven LOW (see Figure 5)                        |      | 4         | μs   |

**Table 5. AC ELECTRICAL CHARACTERISTICS** (All typical values are for  $V_{CC} = 1.8$  V at  $T_A = 25^{\circ}C$  unless otherwise specified.)

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

\_

Table 6. DC CHARACTERISTICS (I<sup>2</sup>C CONTROLLER SDA, SCL)

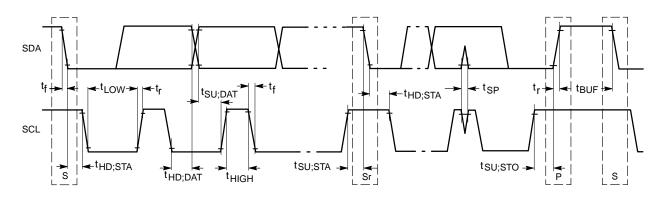

#### **DEFINITION OF TIMING**

Figure 6. Definition of Timing for Full–Speed Mode Devices on the I<sup>2</sup>C Bus

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The FXL6408 I/O expander frees up six ports of the central processor to be dedicated for more critical functions. FXL6408 enables the The addition of eight General-Purpose Input / Output (GPIO) ports to a system processor while using two I/O ports for I<sup>2</sup>C control (net six additional I/Os). The device can be used in multiple applications, from button monitoring to driving control pins of other ICs in the system. It also allows the system designer to add new features and functions quickly without upgrading the central processor. The FXL6408 includes eight I/O pins controlled by an integrated I<sup>2</sup>C slave and allows the central processor to control each I/O independently. When configured as outputs, each pin can deliver up to 6 mA drive. When configured as inputs, the default state can be independently configured. In addition, the FXL6408 has integrated pull-up and pull-down resistors that are enabled via I<sup>2</sup>C commands in the register map. This allows the system designer to pre-bias the inputs to a known level to allow use with un-driven input signals.

#### **Interrupt Operation**

The  $\overline{INT}$  pin is a LOW-asserted open-drain output and requires an external pull-up resistor. The FXL6408 signals an interrupt to the processor when an event occurs, removing the need for the processor to continuously poll the FXL6408 registers. Immediately after detecting a change at an input, the FXL6408 writes the corresponding bit in the input interrupt status register (13<sub>h</sub>) and asserts the  $\overline{INT}$  pin by pulling it LOW. The interrupt status register bit remains HIGH until the processor reads the register and clears the bit. If the input pin remains in the non-default state after the interrupt has been serviced, a new interrupt is not generated until after the input state has first returned to its default state and changed back to its non-default state. The FXL6408 also contains an Input Status register (0F<sub>h</sub>) used to verify the current status of the given input at the time when the interrupt is serviced by the processor. These two registers allow the processor to determine the following information

## Translation

The FXL6408 has the ability to translate between the

Table 9. I

Table 12. OUTPUT STATE (Address  $05_h$ ; if the pin is defined as input in register  $03_h$ , the corresponding bit has no effect)

| Bit # | Name  | Bit Size | Description           |

|-------|-------|----------|-----------------------|

| 7     | Out 7 | 1        | 0: GPIO Output = LOW  |

| 6     | Out 6 | 1        | 1: GPIO Output = HIGH |

| 5     | Out 5 | 1        |                       |

| 4     | Out 4 | 1        |                       |

| 3     | Out 3 | 1        |                       |

| 2     | Out 2 | 1        |                       |

| 1     | Out 1 | 1        |                       |

| 0     | Out 0 | 1        |                       |

Table 13. OUTPUT HIGH-Z (Address 07h; if the pin is defined as input in register 03h, the corresponding bit has no effect)

| Bit # | Name  | Bit Size | Description                                           |

|-------|-------|----------|-------------------------------------------------------|

| 7     | Out 7 | 1        | 0: GPIO Output state follows register 05 <sub>h</sub> |

| 6     | Out 6 | 1        | 1: GPIO Output = HIGH–Z                               |

| 5     | Out 5 | 1        |                                                       |

| 4     | Out 4 | 1        |                                                       |

| 3     | Out 3 | 1        |                                                       |

| 2     | Out 2 | 1        |                                                       |

| 1     | Out 1 | 1        |                                                       |

| 0     |       | -        |                                                       |

|       |       |          |                                                       |

Table 15. PULL ENABLE (Address 0B

**Table 18. INTERRUPT MASK** (Address  $11_h$ ; if the pin is defined as output in register  $03_h$ , the corresponding bit has no effect; this bit enables the interrupt generation from input pin state change to INT)

Bit #

Name

Bit Size

Desce80 Tc(ea5811(56.5754208.743 694.998 .9071 15.351 3185

#### UQFN16 1.80x2.60x0.50, 0.40P CASE 523BF ISSUE A

DATE 06 MAY 2024

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi