nse '

#### **TRUTH TABLE**

| V <sub>IN</sub> | LED | v <sub>o</sub> |

|-----------------|-----|----------------|

| High            | OFF | High           |

| Low             | ON  | Low            |

NOTE: When not communicating,  $\ensuremath{V_{\text{IN}}}$  must be in static high logic condition.

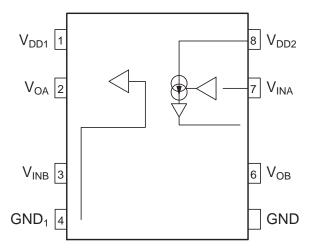

#### **Functional Schematic**

$0.1 \mu F$  bypass capacitor required from  $V_{DD}$  to GND

Figure 1. Functional Schematic

## **ABSOLUTE MAXIMUM RATINGS** ( $T_A = 25^{\circ}C$ unless otherwise specified)

| Symbol           | Parameter           | Value       | Units |

|------------------|---------------------|-------------|-------|

| T <sub>STG</sub> | Storage Temperature | -40 to +125 | ٥     |

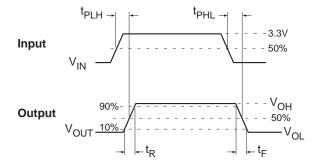

**SWITCHING CHARACTERISTICS** ( $T_A = -40^{\circ}C$  to +110°C, 3.0 V  $\leq$  V $_{DD} \leq$  5.5 V, unless otherwise specified. Apply over all recommended conditions, typical value is measured at V $_{DD1} = V_{DD2} = +3.3$  V,  $T_A = 25^{\circ}C$ )

| Symbol               | Parameter                                                     | Conditions                                                | Min.          | Тур.         | Max.         | Unit          |

|----------------------|---------------------------------------------------------------|-----------------------------------------------------------|---------------|--------------|--------------|---------------|

|                      | Data Rate                                                     |                                                           |               |              | 15           | Mbit/s        |

| t <sub>PHL</sub>     | Propagation Delay Time to Logic Low Output                    | PW = 66.7 ns, C <sub>L</sub> = 15 pF                      |               | 37           | 60           | ns            |

| t <sub>PLH</sub>     | Propagation Delay Time to Logic High Output                   | PW = 66.7 ns, C <sub>L</sub> = 15 pF                      |               | 40           | 60           | ns            |

| PWD                  | Pulse Width Distortion,   t <sub>PHL</sub> - t <sub>PLH</sub> | PW = 66.7 ns, C <sub>L</sub> = 15 pF<br>(Note 5)          |               | 3            | 15           | ns            |

| t <sub>PSK(CC)</sub> | Channel-Channel Skew                                          | PW = 66.7 ns, C <sub>L</sub> = 15 pF<br>(Note 6)          |               | 12           | 25           | ns            |

| t <sub>PSK(PP)</sub> | Part-Part Skew                                                | PW = 66.7 ns, C <sub>L</sub> = 15 pF<br>(Note 7)          |               |              | 30           | ns            |

| t <sub>R</sub>       | Output Rise Time (10% to 90%)                                 | PW = 66.7 ns, C <sub>L</sub> = 15 pF                      |               | 6.5          |              | ns            |

| t <sub>F</sub>       | Output Fall Time (90% to 10%)                                 | PW = 66.7 ns, C <sub>L55.6</sub> 5084 <sub>13q514.4</sub> | 3iof437.443 5 | 82.123 38.20 | 0 8 450.6519 | 9 572.8252 Tr |

| www. |  |

|------|--|

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

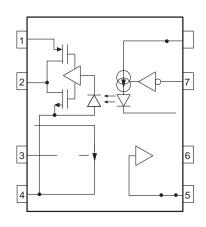

## **TEST CIRCUITS**

Figure 15. Test Circuit for Propagation Delay Time and Rise Time, Fall Time

SOIC8 CASE 751DZ ISSUE O

DATE 30 SEP 2016

| <u> </u> | - |               |   |

|----------|---|---------------|---|

| _        |   | ALL DIMENSION | , |