### http://onsemi.com

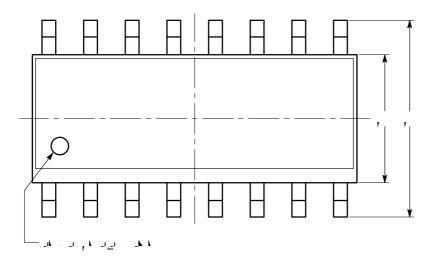

SOIC-16 W SUFFIX CASE 751BG

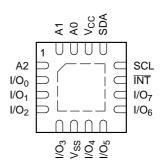

TQFN-16 HV4 SUFFIX CASE 510AE

• These Devices are Pb—Free, Halogen Free/BFR Free and are RoHS Compliant

### **Applications**

- White Goods (dishwashers, washing machines)

- Handheld Devices (cell phones, PDAs, digital cameras)

- Data Communications (routers, hubs and servers)

- 1 All I/Os are set to inputs at RESET.

TQFN 4 x 4 mm (HV4) (Top View)

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 14 of this data sheet.

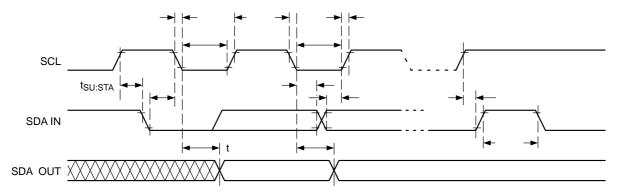

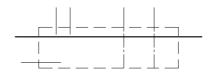

$\textbf{Table 5. A.C. CHARACTERISTICS} \ (V_{CC} = 2.3 \ V \ to \ 5.5 \ V; \ T_{A} = -40 ^{\circ}C \ to \ +85 ^{\circ}C, \ unless \ otherwise \ specified.) \ (Note \ 8)$

|                         |                            | Standard I <sup>2</sup> C |      | Fast I <sup>2</sup> C |     |       |

|-------------------------|----------------------------|---------------------------|------|-----------------------|-----|-------|

| Symbol                  | Parameter                  | Min                       | Max  | Min                   | Max | Units |

| F <sub>SCL</sub>        | Clock Frequency            |                           | 100  |                       | 400 | kHz   |

| t <sub>HD:STA</sub>     | START Condition Hold Time  | 4                         |      | 0.6                   |     | μS    |

| t <sub>LOW</sub>        | Low Period of SCL Clock    | 4.7                       |      | 1.3                   |     | μS    |

| t <sub>HIGH</sub>       | High Period of SCL Clock   | 4                         |      | 0.6                   |     | μs    |

| t <sub>SU:STA</sub>     | START Condition Setup Time | 4.7                       |      | 0.6                   |     | μs    |

| t <sub>HD:DAT</sub>     | Data In Hold Time          | 0                         |      | 0                     |     | μs    |

| t <sub>SU:DAT</sub>     | Data In Setup Time         | 250                       |      | 100                   |     | ns    |

| t <sub>R</sub> (Note 9) | SDA and SCL Rise Time      |                           | 1000 |                       | 300 | ns    |

t<sub>F</sub> (Note 9)

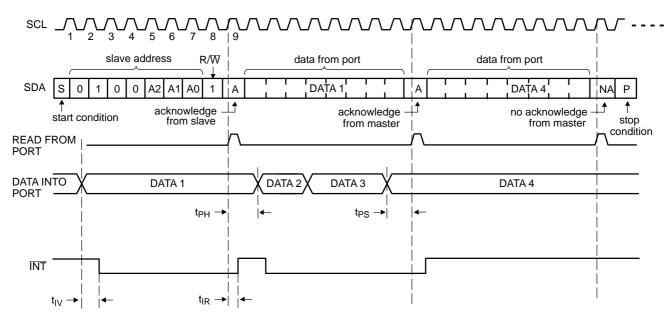

Figure 2. I<sup>2</sup>C Serial Interface Timing

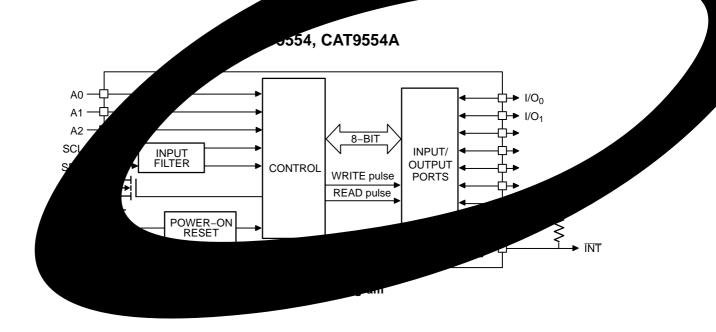

### **INT**: Interrupt Output

The open-drain interrupt output is activated when one of the port pins configured as an input changes state (differs from the corresponding input port register bit state). The interrupt is deactivated when the input returns to its previous state or the input port register is read. Changing an I/O from an output to an input may cause a false interrupt if the state of the pin does not match the contents of the input port register.

| Acknowledge |  |  |

|-------------|--|--|

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

The output port register sets the outgoing logic levels of the I/O ports, defined as outputs by the configuration register. Bit values in this register have no effect on I/O pins defined as inputs. Reads from the output port register reflect the value that is in the flip—flop controlling the output, not the actual I/O pin value.

### Power-On Reset Operation

When the power supply is applied to  $V_{CC}$  pin, an internal power—on reset pulse holds the CAT9554/9554A in a reset state until  $V_{CC}$  reaches  $V_{POR}$  level. At this point, the reset

condition is released and the internal state machine and the CAT9554/9554A registers are initialized to their default state.

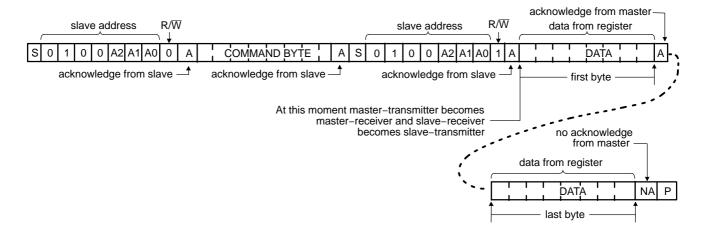

Figure 12. Read from Register

Figure 13. Read Input Port Register

## **PACKAGE DIMENSIONS**

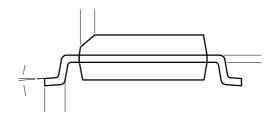

SOIC-16, 150 mils CASE 751BG-01 ISSUE O

### **TOP VIEW**

SIDE VIEW END VIEW

Notes:

# PACKAGE DIMENSIONS

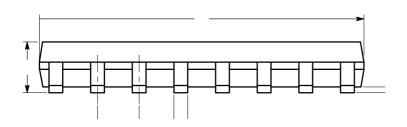

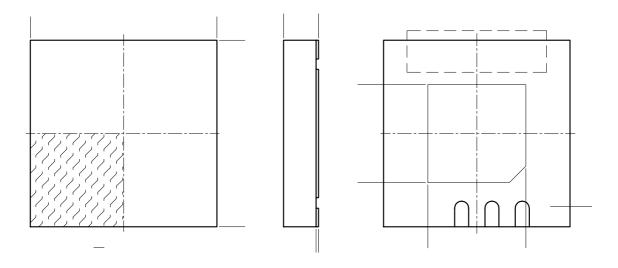

TQFN16, 4x4 CASE 510AE-01 ISSUE A

### **PACKAGE DIMENSIONS**

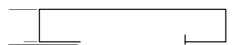

TSSOP16, 4.4x5 CASE 948AN-01 ISSUE O