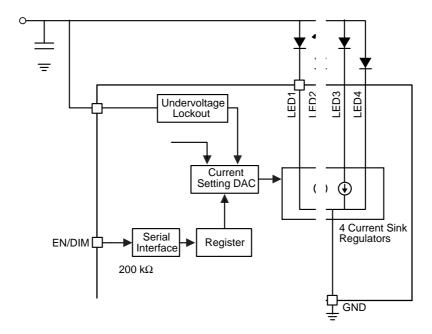

# Description

The CAT4003B and CAT4004B provide respectively three and four matched low dropout current sources to drive LEDs. The CAT400XB requires no external RSET resistor. The LED current is internally set to 25~mA wh

# **MARKING DIAGRAMS**

UDFN8 (2 x 2 mm)

BH = CAT4004B Device Code

A = Assembly Location Code

Y = Production Year (last digit)

M = Production Month: 1 – 9, O, N, D

KL = CAT4003B Device Code

Y = Production Year (last digit)

M = Production Month: 1 - 9, O, N, D

KL = CAT4003B Device CodeA = Assembly Location Code

L4 = CAT4003B Device Code A = Assembly Location Code YW = Year and Work Week

PIN CONNECTIONS (Top View)

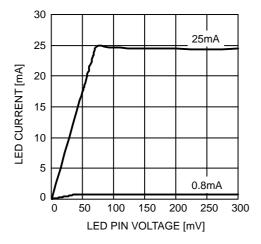

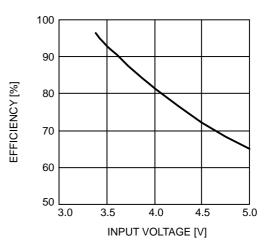

## TYPICAL CHARACTERISTICS

(CAT4003B,  $V_{IN}$  = 4 V,  $V_F$  = 3.3 V,  $I_{OUT}$  = 75 mA (3 LEDs at 25 mA),  $C_{IN}$  = 1  $\mu$ F,  $T_{AMB}$  = 25  $^{\circ}$ C unless otherwise specified.)

Figure 6. Dropout Characteristics

Figure 7. Efficiency vs. Input Voltage

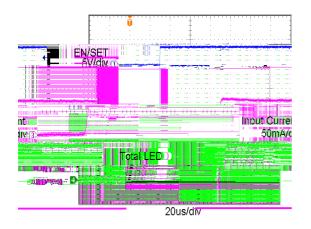

Figure 8. Power Up Waveform

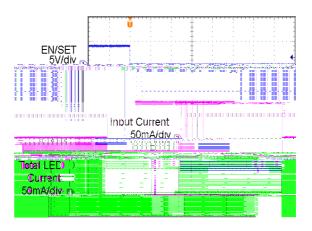

Figure 9. Power Down Waveform

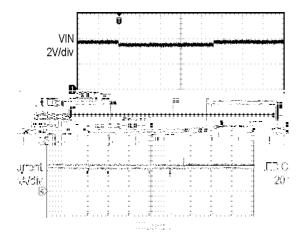

**Figure 10. Line Transient Waveform**

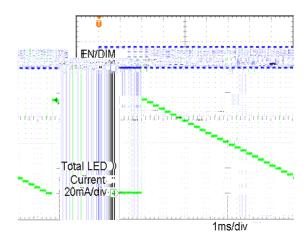

Figure 11. Dimming Levels

### **Pin Functions**

**VIN** is the supply pin for the charge pump. A small 1  $\mu$ F ceramic bypass capacitor is required between the VIN pin and ground near the device. The operating input voltage range is from 2.4 V to 5.5 V. Whenever the input supply falls below the under–voltage threshold (2.0 V), all the LED channels are disabled and the device enters shutdown mode.

**EN/DIM** is the enable and one wire dimming input for all LED channels. Levels of logic high and logic low are set at 1.3 V and 0.4 V respectively. When EN/DIM is initially taken high, the CAT400XB becomes enabled and all LED currents are set to the full scale 25 mA. To place the device

**LED1 to** 1 **ED4** provide the internal regulated current for each of the LED cathodes. The pins enter a high impedance zero currer state whenever the device is placed in shutdown mode.

**GND** is the ground reference for the device. The pin must be connected the ground plane on the PCB.

**TAB** (CAl 004B only) is the exposed pad underneath the package. I r best thermal performance, the tab should be soldered to the PCB and connected to the ground plane.

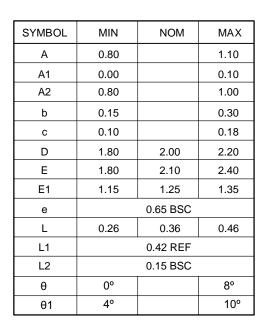

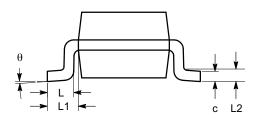

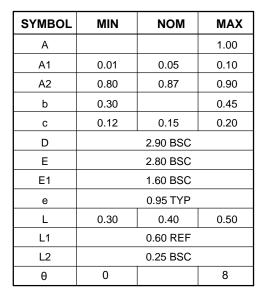

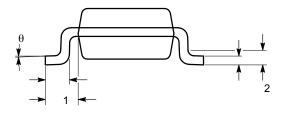

# TSOP-6 3.00x1.50x0.90, 0.95P CASE 318G ISSUE W

DATE 26 FEB 2024

NOTES: 1. DIMENSIONING AND TOLERAN

# TSOP-6 3.00x1.50x0.90, 0.95P

CASE 318G ISSUE W

DATE 26 FEB 2024

# GENERIC MARKING DIAGRAM\*

XXX = Specific Device Code A = Assembly Location Y = Year

W = Work Week

■ Pb-Free Package

| STYLE 1:<br>PIN 1. DRAIN<br>2. DRAIN<br>3. GATE<br>4. SOURCE<br>5. DRAIN<br>6. DRAIN | STYLE 2:<br>PIN 1. EMITTER 2<br>2. BASE 1<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 2<br>6. COLLECTOR 2 | STYLE 3: PIN 1. ENABLE 2. N/C 3. R BOOST 4. Vz 5. V in 6. V out                            | STYLE 4:<br>PIN 1. N/C<br>2. V in<br>3. NOT USED<br>4. GROUND<br>5. ENABLE<br>6. LOAD    | STYLE 5: PIN 1. EMITTER 2 2. BASE 2 3. COLLECTOR 1 4. EMITTER 1 5. BASE 1 6. COLLECTOR 2 | STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR 3. BASE 4. EMITTER 5. COLLECTOR 6. COLLECTOR |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| STYLE 7: PIN 1. COLLECTOR 2. COLLECTOR 3. BASE 4. N/C 5. COLLECTOR 6. EMITTER        | STYLE 8: PIN 1. Vbus 2. D(in) 3. D(in)+ 4. D(out)+ 5. D(out) 6. GND                                        | STYLE 9: PIN 1. LOW VOLTAGE GATE 2. DRAIN 3. SOURCE 4. DRAIN 5. DRAIN 6. HIGH VOLTAGE GATE | STYLE 10:<br>PIN 1. D(OUT)+<br>2. GND<br>3. D(OUT)-<br>4. D(IN)-<br>5. VBUS<br>6. D(IN)+ | STYLE 11: PIN 1. SOURCE 1 2. DRAIN 2 3. DRAIN 2 4. SOURCE 2 5. GATE 1 6. DRAIN 1/GATE 2  | STYLE 12:<br>PIN 1. I/O<br>2. GROUND<br>3. I/O<br>4. I/O<br>5. VCC<br>6. I/O        |

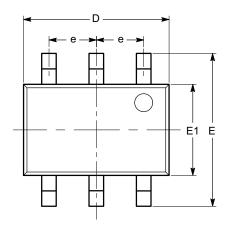

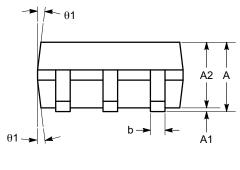

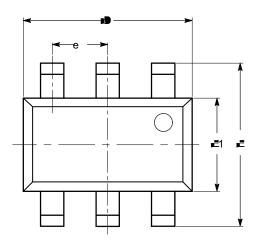

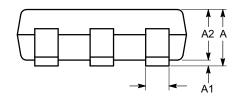

# SC-88 (SC-70 6 Lead), 1.25x2 CASE 419AD ISSUE A

## **DATE 07 JUL 2010**

**TOP VIEW**

SIDE VIEW

END VIEW

## Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MO-203.

# TSOT-23, 6 LEAD CASE 419AF-01 ISSUE O

**DATE 19 DEC 2008**

| T  | OP. | VII | EW |

|----|-----|-----|----|

| 10 | אכ  | VII | ₽W |

# **SIDE VIEW**

### Notes:

(1) A .803 1.93 ■ 1 1.18 e . ≡ (2) C ye w h ■ ■ C -193.

**END VIEW**

| DOCUMENT NUMBER: | 98AON34406E     | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSOT-23. 6 LEAD |                                                                                                                                                                                 | PAGE 1 OF 1 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.