# **Micro-Stepping Motor Driver**

Introduction

The AMIS 30522/NCV70522 is a micro stepping stepper motor driver for bipolar stepper motors. The chip is connected through I/O pins and a SPI interface with an external microcontroller. The AMIS

#### Table of Contents

| Page                                 |

|--------------------------------------|

| Introduction 1                       |

| Features 1                           |

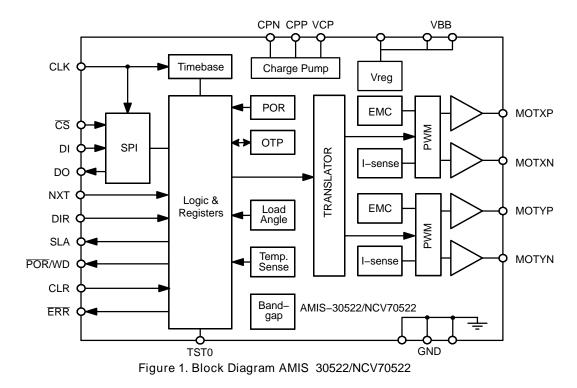

| Block Diagram 3                      |

| Pin Description 3                    |

| Absolute Maximum Ratings 4           |

| Equivalent Schematics 4              |

| Package Thermal Characteristics 5    |

| Thermal Resistance 4                 |

| Electrical Spum nSstancc.rC.i73.254. |

|                                      |

. . . . . . . . . . . . . . . .

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                                      | Min  | Max  | Unit |

|------------------|----------------------------------------------------------------|------|------|------|

| V <sub>BB</sub>  | Analog DC Supply Voltage (Note 1)                              | -0.3 | +40  | V    |

| T <sub>ST</sub>  | Storage Temperature                                            | -55  | +160 | °C   |

| TJ               | Junction Temperature (Note 2)                                  | -50  | +175 | °C   |

| V <sub>ESD</sub> | Electrostatic Discharges on Component Level, All Pins (Note 3) | -2   | +2   | kV   |

| V <sub>ESD</sub> | Electrostatic Discharges on Component Level, HiV Pins (Note 4) | -8   | +8   | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. For limited time < 0.5 s

2. Circuit functionality not guaranteed.

Human Body Model (100 pF via 1.5 kΩ, according to JEDEC EIA–JESD22–A114–B)

HiV = High Voltage Pins MOTxx, V<sub>BB</sub>, GND; Human Body Model (100 pF via 1.5 kΩ, according to JEDEC EIA–JESD22–A114–B)

#### Table 3. THERMAL RESISTANCE

|         | Thermal Resistance      |            |            |      |  |  |

|---------|-------------------------|------------|------------|------|--|--|

|         |                         | Junction t |            |      |  |  |

| Package | Junction to Exposed Pad | 1S0P Board | 2S2P Board | Unit |  |  |

| NQFP-32 | 0.95                    | 60         | 30         | K/W  |  |  |

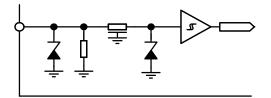

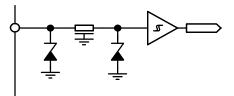

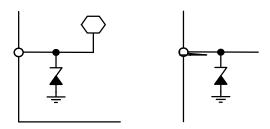

#### EQUIVALENT SCHEMATICS

The following figure gives the equivalent schematics of the user relevant inputs and outputs. The diagrams are simplified representations of the circuits used.

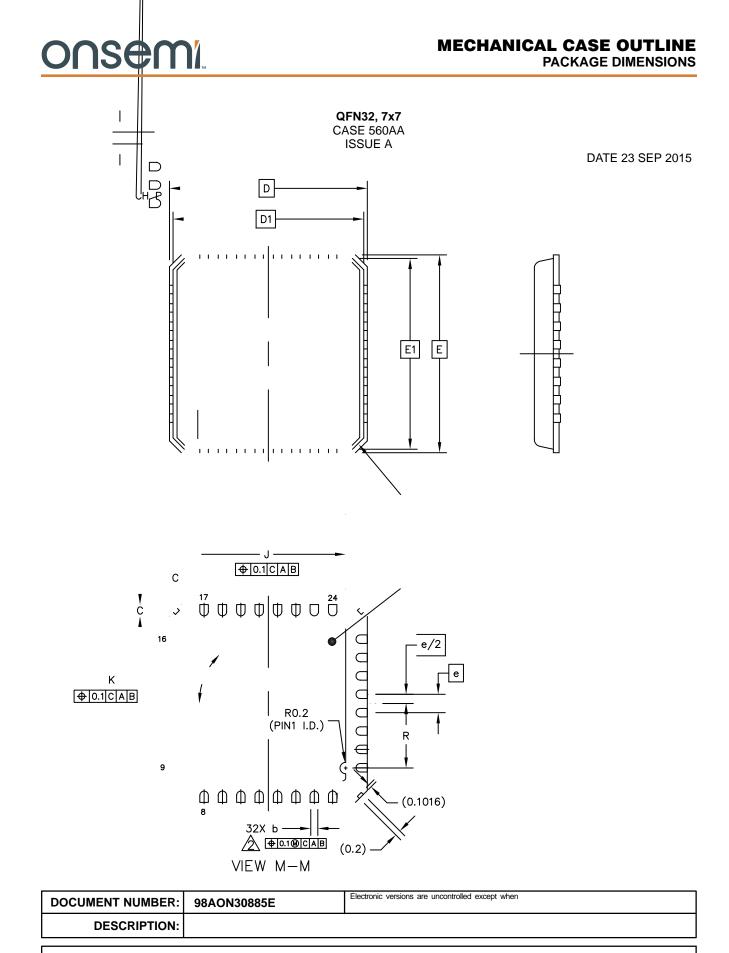

#### PACKAGE THERMAL CHARACTERISTICS

The 522 is available in a NQFP32 package. For cooling optimizations, the NQFP has an exposed thermal pad which has to be soldered to the PCB ground plane. The ground

AMIS

| Table 6. AC PARAMETERS ( | The AC Parameters are Given for $V_{BB}$ and Temperature in Their Operating Ran | qes) |

|--------------------------|---------------------------------------------------------------------------------|------|

|                          |                                                                                 |      |

| Symbol                | Pin(s)     | Parameter                                                 | Remark/Test Conditions                                                                  | Min  | Тур  | Max  | Unit               |

|-----------------------|------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|--------------------|

| INTERNAL              | OSCILLA    | TOR                                                       |                                                                                         |      |      |      |                    |

| f <sub>osc</sub>      |            | Frequency of Internal Oscillator                          |                                                                                         | 3.6  | 4.0  | 4.4  | MHz                |

| MOTORDR               | IVER       |                                                           |                                                                                         |      | •    |      |                    |

|                       |            | PWM Frequency                                             |                                                                                         | 20.8 | 22.8 | 24.8 | kHz                |

| f <sub>PWM</sub>      | MOTxx      | Double PWM Frequency                                      | Frequency Depends Only on<br>Internal Oscillator                                        | 41.6 | 45.6 | 49.6 | kHz                |

| f <sub>d</sub>        |            | PWM Jitter Depth (Note 13)                                |                                                                                         |      | 10   |      | % f <sub>PWM</sub> |

|                       |            |                                                           | EMC[1:0] = 00                                                                           |      | 150  |      | V/μs               |

| th                    | MOTIO      | Turn–On Voltage Slope, 10% to 90%                         | EMC[1:0] = 01                                                                           |      | 100  |      | V/μs               |

| tb <sub>rise</sub>    | MOTxx      | (Note 13)                                                 | EMC[1:0] = 10                                                                           |      | 50   |      | V/μs               |

|                       |            |                                                           | EMC[1:0] = 11                                                                           |      | 25   |      | V/μs               |

|                       |            |                                                           | EMC[1:0] = 00                                                                           |      | 150  |      | V/μs               |

| the                   | MOTxx      | Turn-off Voltage Slope, 90% to 10%                        | EMC[1:0] = 01                                                                           |      | 100  |      | V/μs               |

| tb <sub>fall</sub>    | WICTXX     | (Note 13)                                                 | EMC[1:0] = 10                                                                           |      | 50   |      | V/μs               |

|                       |            |                                                           | EMC[1:0] = 11                                                                           |      | 25   |      | V/μs               |

| DIGITAL O             | UTPUTS     |                                                           |                                                                                         |      |      |      |                    |

| t <sub>H2L</sub>      | DO<br>ERR  | Output Falltime from $V_{\text{inH}}$ to $V_{\text{inL}}$ | Capacitive Load 400 pF and Pullup Resistor of 1.5 $k\Omega$                             |      |      | 50   | ns                 |

| CHARGE P              | UMP        |                                                           |                                                                                         |      |      |      |                    |

| f <sub>CP</sub>       | CPN<br>CPP | Charge Pump Frequency                                     |                                                                                         |      | 250  |      | kHz                |

| t <sub>CPU</sub>      | MOTxx      | Startup Time of Charge Pump (Note 14)                     | Spec External Components                                                                |      |      | 5.0  | ms                 |

| CLR FUNC              | TION       | · · · · · ·                                               |                                                                                         |      |      |      |                    |

| t <sub>CLR</sub>      | CLR        | Minimum Time for Hard Reset                               |                                                                                         | 100  |      |      | μs                 |

| NXT FUNC              | TION       |                                                           |                                                                                         |      |      |      |                    |

| t <sub>NXT_HI</sub>   |            | NXT Minimum, High Pulse Width                             | See Figure 4                                                                            | 2.0  |      |      | μs                 |

| t <sub>NXT_LO</sub>   |            | NXT Minimum, Low Pulse Width                              | See Figure 4                                                                            | 2.0  |      |      | μs                 |

| t <sub>DIR_SET</sub>  | NXT        | NXT Hold Time, Following<br>Change of DIR                 | See Figure 4                                                                            |      | 2.0  |      | μs                 |

| t <sub>DIR_HOLD</sub> |            | NXT Hold Time, Before Change of DIR                       | See Figure 4                                                                            |      | 2.0  |      | μs                 |

| POWER UF              | 0          |                                                           |                                                                                         |      |      |      |                    |

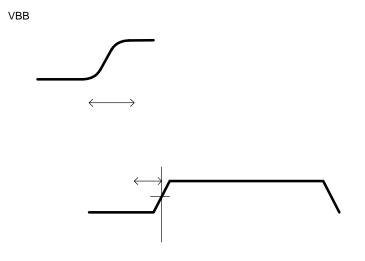

| t <sub>PU</sub>       |            | Power–Up Time                                             | $V_{BB} = 12 \text{ V}, \text{ I}_{LOAD} = 50 \text{ mA}, \\ C_{LOAD} = 220 \text{ nF}$ |      |      | 110  | μs                 |

| t <sub>PD</sub>       | PORB/      | Power–Down Time                                           | external conditions                                                                     |      |      |      | ms                 |

| t <sub>POR</sub>      | WD         | Reset Duration                                            |                                                                                         |      | 100  |      | ms                 |

| t <sub>RF</sub>       | 1          | Reset Filter Time                                         |                                                                                         |      | 1.0  |      | μs                 |

| WATCHDO               | G          | <u> </u>                                                  |                                                                                         | •    | -    | •    | -                  |

| t <sub>WDTO</sub>     |            | Watchdog Time Out Interval                                |                                                                                         | 32   |      | 512  | ms                 |

|                       |            |                                                           |                                                                                         |      | 1    |      | 1                  |

13. Characterization Data Only 14. Guaranteed by design.

#### FUNCTIONAL DESCRIPTION

#### H Bridge Drivers

transistors

A full H bridge is integrated for each of the two stator windings. Each H bridge consists of two low side and two high side N type MOSFET switches. Writing logic '0' in bit <MOTEN> disables all drivers (High Impedance). Writing logic '1' in this bit enables both bridges and current can flow in the motor stator windings.

In order to avoid large currents through the H bridge switches, it is guaranteed that the top and bottom switches of the same half bridge are never conductive simultaneously (interlock delay).

A two stage protection against shorts on motor lines is implemented. In a first stage, the current in the driver is limited. Secondly, when excessive voltage is sensed across the transistor, the transistor is switched off.

In order to reduce the radiated/conducted emission, voltage slope control is implemented in the output switches. The output slope is defined by the gate drain capacitance of output transistor and the (limited) current that drives the gate. There are two trimming bits for slope control (See Table 12 SPI Control Parameter Overview EMC[1:0]).

The power transistors are equipped with so called "active diodes": when a current is forced through the transistor switch in the reverse direction, i.e. from source to drain, then the transistor is switched on. This ensures that most of the current flows through the channel of the transistor instead of through the inherent parasitic drain bulk diode of the transistor.

Depending on the desired current range and the micro step position at hand, the  $R_{DS(on)}$  of the low side

|          |      | % of | I <sub>max</sub> |     |     |        |        |

|----------|------|------|------------------|-----|-----|--------|--------|

|          | 000  | 001  | 010              | 011 | 100 |        |        |

| MSP[6:0] | 1/32 | 1/16 | 1/8              | 1/4 | 1/2 | Coil x | Coil y |

| 000 0000 | '0'  | 0*   | 0*               | 0*  | 0*  | 0      | 100    |

#### Table 10. CIRCULAR TRANSLATOR TABLE

#### Table 10. CIRCULAR TRANSLATOR TABLE

| Stepmode (SM[2:0]) |      |      |     |     |     |        | I <sub>max</sub> |

|--------------------|------|------|-----|-----|-----|--------|------------------|

|                    | 000  | 001  | 010 | 011 | 100 |        |                  |

| MSP[6:0]           | 1/32 | 1/16 | 1/8 | 1/4 | 1/2 | Coil x | Coil y           |

| 011 1111           | 63   | _    | _   | _   | -   | 3.5    | -98.8            |

| 100 0000           | 64   | 32   | 16  | 8   | 4   | 0      | -100             |

| 100 0001           | 65   | -    | -   | -   | -   | -3.5   | -98.8            |

| 100 0010           | 66   | 33   | _   | _   | -   | -8.1   | -97.7            |

| 100 0011           | 67   | -    | -   | _   | -   | -12.7  | -96.5            |

| 100 0100           | 68   | 34   | 17  | _   | -   | -17.4  | -95.3            |

| 100 0101           | 69   | _    | _   | _   | -   |        |                  |

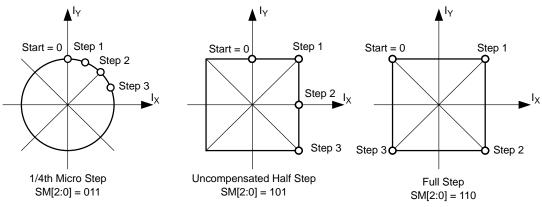

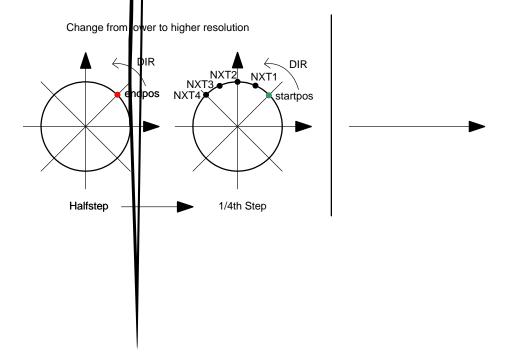

Figure 9. Translator Table: Circular and Square

#### Direction

The direction of rotation is selected by means of following combination of the DIR input pin and the SPI controlled direction bit <DIRCTRL> as illustrated in Table 12.

#### NXT Input

Changes on the NXT input will move the motor current one step up/down in the translator table (even when the motor is disabled). Depending on the NXT polarity bit <NXTP>

exist per electrical period, yielding in total 4 zero current observation points per electrical period.

AMIS

#### SPI INTERFACE

The serial peripheral interface (SPI) allows an external microcontroller (Master) to communicate with the 522. The implemented SPI block is designed to interface directly with numerous micro controllers from several manufacturers. The 522 acts always as a Slave and cannot initiate any transmission. The operation of the device is configured and controlled by means of SPI registers which are observable for read and/or write from the Master.

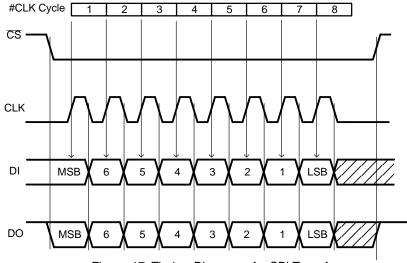

#### SPI Transfer Format and Pin Signals

During a SPI transfer, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (CLK) synchronizes shifting and sampling of the information on the two serial data lines (DO and DI). DO signal is the output from the Slave (522), and DI signal is the output from the Master. A chip select line ( $\overline{CS}$ ) allows individual selection of a Slave SPI device in a multiple slave system. The  $\overline{CS}$  line is active low. If the 522 is not selected, DO is pulled up with the external pullup resistor. Since 522 operates as a Slave in MODE 0 (CPOL = 0; CPHA = 0) it always clocks data out on the falling edge and samples data in on rising edge of clock. The Master SPI port must be configured in MODE 0 too, to match this operation. The SPI clock idles low between the transferred bytes.

The diagram below is both a Master and a Slave timing diagram since CLK, DO and DI pins are directly connected between the Master and the Slave.

Figure 17. Timing Diagram of a SPI Transfer

NOTE: At the falling edge of the eighth clock pulse the data–out shift register is updated with the content of the addressed internal SPI register. The internal SPI registers are updated at the first rising edge of the 522 system clock when  $\overline{CS}$  = High.

AMIS

#### Table 16. SPI STATUS FLAGS OVERVIEW

| Mnemonic | Flag                                                   | Length<br>(bit) | Related<br>SPI Register | Comment                                                                                                                                                                                                                                                                                                             | Reset<br>State |

|----------|--------------------------------------------------------|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CPFail   | Charge Pump Failure                                    | 1               | Status Register 0       | <ul> <li>'0' = no failure</li> <li>'1' = failure: indicates that the charge pump does not reach the required voltage level.</li> </ul>                                                                                                                                                                              | '0'            |

| WD       | Watchdog event                                         | 1               | Status Register 0       | This bit indicates the watchdog timer has not been<br>cleared properly in time. If the master reads that WD<br>is set to "1" after reset, it means that a watchdog re-<br>set occurred (warm boot) instead of power-on-reset<br>(cold boot). WD bit will be cleared only when the<br>master writes "0" to WDEN bit. | ʻ0'            |

| MSP[6:0] | Micro Step Position                                    | 7               | Status Register 3       | Translator micro step position                                                                                                                                                                                                                                                                                      | ʻ0000000'      |

| OPENX    | OPEN Coil X                                            | 1               | Status Register 0       | '1' = Open coil detected                                                                                                                                                                                                                                                                                            | '0'            |

| OPENY    | OPEN Coil Y                                            | 1               | Status Register 0       | '1' = Open coil detected                                                                                                                                                                                                                                                                                            | '0'            |

| OVCXNB   | Overcurrent at<br>MOTXN Terminal;<br>Bottom Transistor | 1               | Status Register 1       | <ul> <li>'0' = no failure</li> <li>'1' = failure: indicates that overcurrent is detected at bottom transistor XN-terminal</li> </ul>                                                                                                                                                                                | ʻ0'            |

| OVCXNT   | Overcurrent at<br>MOTXN Terminal;<br>Top Transistor    | 1               | Status Register 1       | '0' = no failure<br>'1' = failure: indicates that overcurrent is detected at<br>top transistor XN-terminal                                                                                                                                                                                                          | '0'            |

| OVCXPB   | Overcurrent at<br>MOTXP Terminal;<br>Bottom Transistor | 1               | Status Register 1       | '0' = no failure<br>'1' = failure: indicates that overcurrent is detected at<br>bottom transistor XP-terminal                                                                                                                                                                                                       | '0'            |

| OVCXPT   | Overcurrent at<br>MOTXP Terminal;<br>Top Transistor    | 1               | Status Register 1       | '0' = no failure<br>'1' = failure: indicates that overcurrent is detected at<br>top transistor XP-terminal                                                                                                                                                                                                          | '0'            |

| OVCYNB   | Overcurrent at<br>MOTYN Terminal;<br>Bottom Transistor | 1               | Status Register 2       | '0' = no failure<br>'1' = failure: indicates that overcurrent is detected at<br>bottom transistor YN-terminal                                                                                                                                                                                                       | '0'            |

| OVCYNT   | Overcurrent at<br>MOTYN Terminal;<br>Top Transistor    | 1               | Status Register 2       | '0' = no failure<br>'1' = failure: indicates that overcurrent is detected at<br>top transistor YN-terminal                                                                                                                                                                                                          | ʻ0'            |

| OVCYPB   | Overcurrent at<br>MOTYP Terminal;<br>Bottom Transistor | 1               | Status Register 2       |                                                                                                                                                                                                                                                                                                                     |                |

#### DEVICE ORDERING INFORMATION

| Part Number       | Ambient<br>Temperature Range | Package Type         | Peak<br>Current | Shipping <sup>†</sup> |

|-------------------|------------------------------|----------------------|-----------------|-----------------------|

| AMIS30522C5222RG  | -40°C to +125°C              | NQFP-32<br>(Pb-Free) | 1500 mA         | Tape & Reel           |

| AMIS30522C5222G   | -40°C to +125°C              | NQFP-32<br>(Pb-Free) | 1500 mA         | Tube / Tray           |

| NCV70522MN003R2G* | -40°C to +125°C              | NQFP-32<br>(Pb-Free) | 1500 mA         | Tape & Reel           |

| NCV70522MN003G*   | -40°C to +125°C              | NQFP-32<br>(Pb-Free) | 1500 mA         | Tube / Tray           |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. \*Qualified for automotive applications.

onsemi and are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi