# Dual Bootstrapped, 12 V MOSFET Driver with Output Disable

The ADP3120A is a single Phase 12 V MOSFET gate drivers optimized to drive the gates of both high-side and low-side power MOSFETs in a synchronous buck converter. The high-side and low-side driver is capable of driving a 3000 pF load with a 45 ns propagation delay and a 25 ns transition time.

With a wide operating voltage range, high or low side MOSFET gate drive voltage can be optimized for the best efficiency. Internal adaptive nonoverlap circuitry further reduces switching losses by preventing simultaneous conduction of both MOSFETs.

The floating top driver design can accommodate VBST voltages as high as 35 V, with transient voltages as high as 40 V. Both gate outputs can be driven low by applying a low logic level to the Output Disable  $(\overline{OD})$  pin. An Undervoltage Lockout function ensures that both driver outputs are low when the supply voltage is low, and a Thermal Shutdown function provides the IC with overtemperature protection.

#### **Features**

- All-In-One Synchronous Buck Driver

- Bootstrapped High-Side Drive

- One PWM Signal Generates Both Drives

- Anticross Conduction Protection Circuitry

- OD for Disabling the Driver Outputs Meets CPU VR Requirement when Used with Patented FlexMode™ Controller

- These are Pb-Free Devices

#### **Applications**

- Multiphase Desktop CPU Supplies

- Single-Supply Synchronous Buck Converters

MARKING DIAGRAMS

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb–Free Package

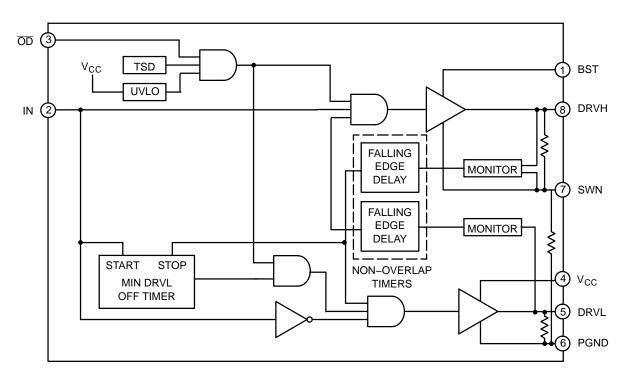

Figure 1. Block Diagram

### **PIN DESCRIPTION**

| SO-8 | DFN8 | Symbol          | Description                                                                                                                                                                                                                                                                        |  |  |

|------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | 1    | BST             | Upper MOSFET Floating Bootstrap Supply. A capacitor connected between BST and SW pins holds this bootstrap voltage for the high–side MOSFET as it is switched. The recommended capacitor value is between 100 nF and 1.0 $\mu$ F. An external diode is required with the ADP3120A. |  |  |

| 2    | 2    | IN              | Logic-Level Input. This pin has primary control of the drive outputs.                                                                                                                                                                                                              |  |  |

| 3    | 3    | OD              | Output Disable. When low, normal operation is disabled forcing DRVH and DRVL low.                                                                                                                                                                                                  |  |  |

| 4    | 4    | V <sub>CC</sub> | Input Supply. A 1.0 μF ceramic capacitor should be connected from this pin to PGND.                                                                                                                                                                                                |  |  |

| 5    | 5    | DRVL            | Output drive for the lower MOSFET.                                                                                                                                                                                                                                                 |  |  |

| 6    | 6    | PGND            | Power Ground. Should be closely connected to the source of the lower MOSFET.                                                                                                                                                                                                       |  |  |

| 7    | 7    | SWN             | Switch Node. Connect to the source of the upper MOSFET.                                                                                                                                                                                                                            |  |  |

| 8    | 8    | DRVH            | Output drive for the upper MOSFET.                                                                                                                                                                                                                                                 |  |  |

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                            | Value                   | Unit                   |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----------------------|

| Operating Ambient Temperature, T <sub>A</sub>                                                                                                                                                                                                                                     |                         | -20 to 85              | °C                   |

| Operating Junction Temperature, T <sub>J</sub> (Note 1)                                                                                                                                                                                                                           |                         | -20 to 150             | °C                   |

| Package Thermal Resistance: SO–8<br>Junction–to–Case, $R_{\theta JC}$<br>Junction–to–Ambient, $R_{\theta JA}$ (2–Layer Board)<br>Package Thermal Resistance: DFN8 (Note 2)<br>Junction–to–Case, $R_{\theta JC}$ (From die to exposed pad)<br>Junction–to–Ambient, $R_{\theta JA}$ |                         | 45<br>123<br>7.5<br>55 | °C/W<br>°C/W<br>°C/W |

| Storage Temperature Range, T <sub>S</sub>                                                                                                                                                                                                                                         |                         | -65 to 150             | °C                   |

| Lead Temperature Soldering (10 sec): Reflow (SMD styles only)                                                                                                                                                                                                                     | Pb-Free (Note 3)        | 260 peak               | °C                   |

| JEDEC Moisture Sensitivity Level                                                                                                                                                                                                                                                  | SO-8 (260 peak profile) | 1                      | _                    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- Internally limited by thermal shutdown, 150°C min.

2 layer board, 1 in<sup>2</sup> Cu, 1 oz thickness.

- 3. 60–180 seconds minimum above 237°C.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

#### **MAXIMUM RATINGS**

| F | Pin Symbol                         | Pin Name                  | V <sub>MAX</sub>                         | V <sub>MIN</sub> |

|---|------------------------------------|---------------------------|------------------------------------------|------------------|

|   | V <sub>CC</sub>                    | Main Supply Voltage Input | 15 V                                     | -0.3 V           |

|   | PGND                               | Ground                    | 0 V                                      | 0 V              |

|   | BST Bootstrap Supply Voltage Input |                           | 35 V wrt/PGND<br>40 V < 50 ns wrt/PGNDC. |                  |

#### **APPLICATIONS INFORMATION**

#### **Theory of Operation**

The ADP3120A are single phase MOSFET drivers designed for driving two N-channel MOSFETs in a synchronous buck converter topology. The ADP3120A will operate from 5.0 V or 12 V, but have been optimized for high current multi-phase buck regulators that convert 12 V rail directly to the core voltage required by complex logic chips. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each driver is capable of driving a 3 nF load at frequencies up to 1 MHz.

#### Low-Side Driver

The low-side driver is designed to drive a ground-referenced low RDS(on) N-Channel MOSFET. The voltage rail for the low-side driver is internally connected to the VCC supply and PGND.

#### **High-Side Driver**

The high–side driver is designed to drive a floating low RDS(on) N–channel MOSFET. The gate voltage for the high side driver is developed by a bootstrap circuit referenced to Switch Node (SW) pin.

The bootstrap circuit is comprised of an external diode, and an external bootstrap capacitor. When the ADP3120A are starting up, the SW pin is at ground, so the bootstrap capacitor will charge up to VCC through the bootstrap diode See Figure 4. When the PWM input goes high, the high–side driver will begin to turn on the high–side MOSFET using the stored charge of the bootstrap capacitor. As the high–side MOSFET turns on, the SW pin will rise. When the high–side MOSFET is fully on, the switch node will be at 12 V, and the BST pin will be at 12 V plus the charge of the bootstrap capacitor (approaching 24 V).

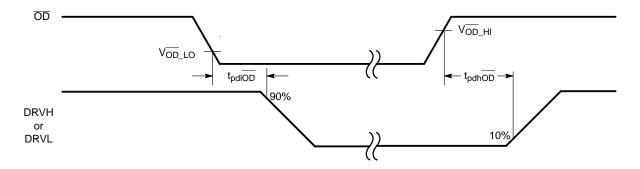

Figure 2. Output Disable Timing Diagram

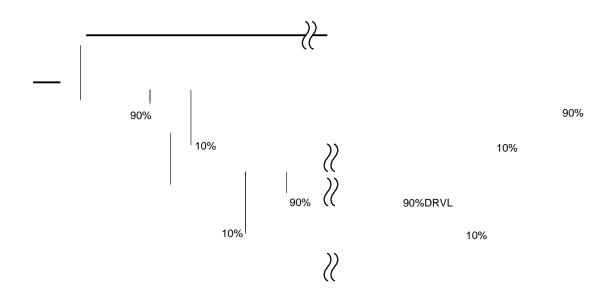

Figure 3. Nonoverlap Timing Diagram