# Low Cost Microprocessor System Temperature Monitor Microcomputer

The ADM1021A is a two-channel digital thermometer and under/overtemperature alarm, intended for use in personal computers and other systems requiring thermal monitoring and management. The device can measure the temperature of a microprocessor using a diode-connected PNP transistor, which can be provided on-chip with the Pentium III or similar processors, or can be a low cost discrete NPN/PNP device, such as the 2N3904/2N3906. A novel measurement technique cancels out the absolute value of the transistor's base emitter

#### Table 4. ELECTRICAL CHARACTERISTICS (continued)

$(T_A = T_{MIN} \text{ to } T_{MAX}, V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}, \text{ unless otherwise noted})$  (Note 1)

| Parameter                                                      | Test Conditions/Comments                    | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------|---------------------------------------------|------|-----|------|------|

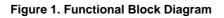

| SMBus Interface (See Figure 2)                                 |                                             |      |     |      |      |

| Logic Input High Voltage, V <sub>IH</sub><br>STBY, SCLK, SDATA | V <sub>DD</sub> = 3.0 V to 5.5 V            | 2.2  | -   | -    | V    |

| Logic Input Low Voltage, V <sub>IL</sub><br>STBY, SCLK, SDATA  | V <sub>DD</sub> = 3.0 V to 5.5 V            | -    | -   | 0.8  | V    |

| SMBus Output Low Sink Current                                  | SDATA Forced to 0.6 V                       | 6.0  | -   | _    | mA   |

| ALERT Output Low Sink Current                                  | ALERT Forced to 0.4 V                       | 1.0  | -   | -    | mA   |

| Logic Input Current, I <sub>IH</sub> , I <sub>IL</sub>         |                                             | -1.0 | -   | +1.0 | μΑ   |

| SMBus Input Capacitance, SCLK, SDATA                           |                                             | _    | 5.0 | _    | pF   |

| SMBus Clock Frequency                                          |                                             | _    | -   | 100  | kHz  |

| SMBus Clock Low Time, t <sub>LOW</sub>                         | t <sub>LOW</sub> between 10% Points         | 4.7  | -   | -    | μs   |

| SMBus Clock High Time, t <sub>HIGH</sub>                       | t <sub>HIGH</sub> between 90% Points        | 4.0  | -   | -    | μs   |

| SMBus Start Condition Setup Time,<br>t <sub>SU:STA</sub>       |                                             | 4.7  | -   | _    | μs   |

| SMBus Repeat Start Condition                                   |                                             | 250  | -   | _    | ns   |

| Setup Time, t <sub>SU:STA</sub>                                | Between 90% and 90% Points                  | 250  | -   | -    | ns   |

| SMBus Start Condition Hold Time, t <sub>HD:STA</sub>           | Time from 10% of SDATA to 90% of SCLK       |      | -   | -    | μs   |

| SMBus Stop Condition Setup Time, t <sub>SU:STO</sub>           | Time from 90% of SCLK to 10% of SDATA       |      | -   | -    | μs   |

| SMBus Data Valid to SCLK                                       | Time for 10% or 90% of SDATA to 10% of SCLK | 250  | -   | _    | ns   |

| Rising Edge Time, t <sub>SU:DAT</sub>                          | Time for 10% or 90% of SDATA to 10% of SCLK | 250  | -   | -    | ns   |

| SMBus Data Hold Time, t <sub>BUF:DAT</sub>                     |                                             | 0    | -   | -    | μs   |

| SMBus Bus Free Time, t <sub>BUF</sub>                          | Between Start/Stop Condition                | 4.7  | -   | -    | μs   |

| SCLK Falling Edge to SDATA                                     |                                             | -    | -   | 1    | μs   |

| Valid Time, t <sub>VD:DAT</sub>                                | Master Clocking in Data                     | -    | -   | 1    | μs   |

1.  $T_{MAX} = 100 \text{ C}$ ,  $T_{MIN} = 0 \text{ C}$ 2. Operation at  $V_{DD} = 5.0 \text{ V}$  guaranteed by design; not production tested. 3. Guaranteed by design; not production tested.

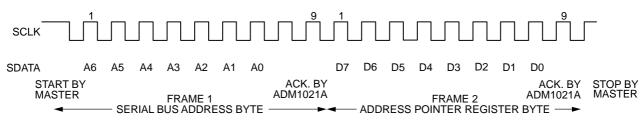

Figure 2. Serial Bus Timing

### **TYPICAL PERFORMANCE CHARACTERISTICS**

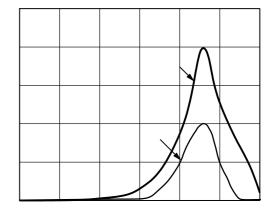

#### Figure 3. Temperature Error vs. PC Board Track Resistance

Figure 5. Temperature Error vs. Common-mode Noise Frequency Figure 6. Temperature Error vs. Pentium<sup>®</sup> III Temperature

Figure 4. Temperature Error vs. Power Supply Noise Frequency

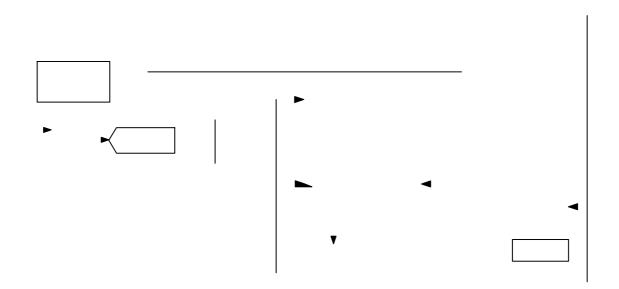

#### **Functional Description**

The ADM1021A contains a two-channel A-to-D converter with special input-signal conditioning to enable operation with remote and on-chip diode temperature sensors. When the ADM1021A is operating normally, the A-to-D converter operates in free-running mode. The analog input multiplexer alternately selects either the on-chip temperature sensor to measure its local temperature or the remote temperature sensor. These signals are digitized by the ADC and the results stored in the local and remote temperature value registers as 8-bit, twos complement words.

The measurement results are compared with local and remote, high and low temperature limits, stored in four on-chip registers. Out-of-limit comparisons generate flags that are stored in the status register, and one or more out-of-limit results will cause the <u>ALERT</u> output to pull low.

The limit registers can be programmed and the device controlled and configured via the serial System Management Bus (SMBus). The contents of any register can also be read back via the SMBus.

Control and configuration functions consist of: Switching the Device between Normal Operation and Standby Mode

Masking or Enabling the ALERT Output Selecting the Conversion Rate On initial powerup, the remote and local temperature values default to -128 C. Since the device normally powers

If the local and/or remote temperature measurement is above the corresponding high temperature limit or below the corresponding low temperature limit, then one or more of these flags are set. Bit 2 is a flag that is set if the remote temperature sensor is open-circuit. These five flags are NOR'd togetheri,5( that)-11.9( if)-11.9( any)-11.[of)-12.1( them)-11( are)-11( high,)-11.7( the)-10.5( ALER)65.3(T)]TET263.112 678.898 31.

#### Table 11. DEVICE ADDRESSES (Note 1)

| ADD0 | ADD1 | Device Address |

|------|------|----------------|

| 0    | 0    | 0011 000       |

| 0    | NC   | 0011 001       |

| 0    | 1    | 0011 010       |

| NC   | 0    | 0101 001       |

| NC   | NC   | 0101 010       |

| NC   | 1    | 0101 011       |

| 1    | 0    | 1001 100       |

| 1    | NC   | 1001 101       |

| 1    | 1    | 1001 110       |

1. ADD0 and ADD1 are sampled at powerup only.

The serial bus protocol operates as follows:

The master initiates data transfer by establishing a start condition, defined as a high-to-low transition on the serial data line SDATA, while the serial clock line SCLK remains high. This indicates that an address/data stream will follow. All slave peripherals connected to the serial bus respond to the START condition and shift in the next eight bits, consisting of a 7-bit address (MSB first) plus an R/W1

Figure 15. Writing to the Address Pointer Register Only

5. Once the ADM1021A has responded to the alert response address, it resets its ALERT output, provided that the error condition that caused the ALERT no longer exists. If the SMBALERT line remains low, the master sends the ARA again, and so on until all devices whose ALERT outputs were low have responded.

#### Low Power Standby Modes

The ADM1021A can be put into a low power standby mode using hardware or software, that is, by taking the STBY input low, or by setting Bit 6 of the configuration register. When STBY is high or Bit 6 is low, the ADM1021A operates normally. When STBY is pulled low or Bit 6 is high, the ADC is inhibited, so any conversion in progress is terminated without writing the result to the corresponding value register.

The SMBus is still enabled. Power consumption in the standby mode is reduced to less than 10  $\mu$ A if there is no SMBus activity or 100  $\mu$ A if there are clock and data signals on the bus.

These two modes are similar but not identical. When <u>STBY</u> is low, conversions are completely inhibited. When Bit 6 is set but <u>STBY</u> is high, a one-shot conversion of both channels can be initiated by writing 0xXX to the one-shot register (Address 0x0F).

#### **Sensor Fault Detection**

The ADM1021A has a fault detector at the D+ input that detects if the external sensor diode is open-circuit. This is a simple voltage comparator that trips if the voltage at D+ exceeds  $V_{CC} - 1.0 \text{ V}$  (typical). The output of this comparator is checked when a conversion is initiated and sets Bit 2 of the status register if a fault is detected.

If the remote sensor voltage falls below the normal measuring range, for example due to the diode being short-circuited, the ADC outputs 128 C (1000 0000). Since the normal operating temperature range of the device only extends down to 0 C, this output code is never seen in

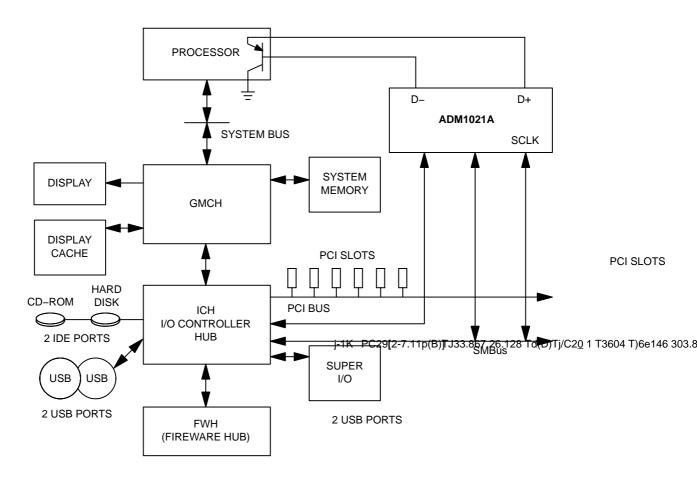

ADM1021A

Figure 20. Typical System Using ADM1021A

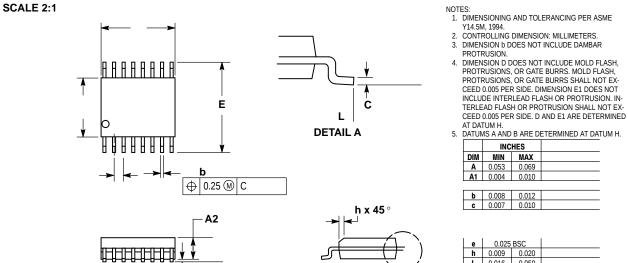

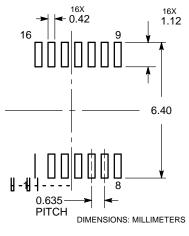

QSOP16 CASE 492-01 ISSUE A

**DETÁIL A**

INCHES

DIM

MIN

MAX

A

0.053

0.069

A1

0.004

0.010

b

0.008

0.012

c

0.007

0.010

0.025 BSC 1

| L | е | 0.025 BSC |       |  |

|---|---|-----------|-------|--|

|   | h | 0.009     | 0.020 |  |

|   | L | 0.016     | 0.050 |  |

| Ĩ |   |           |       |  |

| L | М | 0 °       | 8°    |  |

| XXXXX | = Specific Device Code |

|-------|------------------------|

| YY    | = Year                 |

| WW    | = Work Week            |

| G     | = Pb-Free Package      |

SOLDERING FOOTPRINT

A1

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi