## Hex Inverter with Schmitt Trigger Input

# 14

## 74AC14, 74ACT14

The 74AC14 and 74ACT14 contain six inverter gates each with a Schmitt trigger input. They are capable of transforming slowly changing input signals into sharply defined, jitter–free output signals. In addition, they have a greater noise margin than conventional inverters.

The 74AC14 and 74ACT14 have hysteresis between the positive–going and negative–going input thresholds (typically 1.0 V) which is determined internally by transistor ratios and is essentially insensitive to temperature and supply voltage variations.

- I<sub>CC</sub> Reduced by 50%

- Outputs Source/Sink 24 mA

- 74ACT14 has TTL-Compatible Inputs

- These are Pb–Free Devices

| Supply Voltage                                                                      | V <sub>CC</sub>                     | -0.5 to +6.5                     | V  |

|-------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|----|

| DC Input Diode Current<br>$V_I = -0.5 \text{ V}$<br>$V_I = V_{CC} + 1.5 \text{ V}$  | I <sub>IK</sub>                     | -20<br>+20                       | mA |

| DC Input Voltage                                                                    | V <sub>I</sub>                      | –0.5 to<br>V <sub>CC</sub> + 1.5 | V  |

| DC Output Diode Current<br>$V_O = -0.5 \text{ V}$<br>$V_O = V_{CC} + 0.5 \text{ V}$ | I <sub>OK</sub>                     | -20<br>+20                       | mA |

| DC Output Voltage                                                                   | V <sub>O</sub>                      | -0.5 to<br>V <sub>CC</sub> + 0.5 | V  |

| DC Output Source or Sink Current                                                    | I <sub>O</sub>                      | ±50                              | mA |

| DC V <sub>CC</sub> or Ground Current per Output Pin                                 | I <sub>CC</sub> or I <sub>GND</sub> | ±50                              | mA |

| Storage Temperature Range                                                           | T <sub>STG</sub>                    | -65 to +150                      | °C |

| Junction Temperature                                                                | TJ                                  | 140                              | °C |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

XXXXXX AWLYWW

| V <sub>CC</sub> | Supply Voltage<br>AC |  |  |

|-----------------|----------------------|--|--|

|                 | ACT                  |  |  |

| 1.4 | V |

|-----|---|

| 1.6 |   |

| 0.4 | V |

| 0.5 |   |

| 2.0 | V |

| 2.0 |   |

| 0.8 | V |

|     |   |

|   |   | (Note 6)  | ۰ | <b>-</b> ° | ٥ |  |

|---|---|-----------|---|------------|---|--|

| Į | 1 | (11010 0) | ı |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

|   |   |           |   |            |   |  |

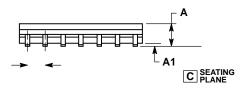

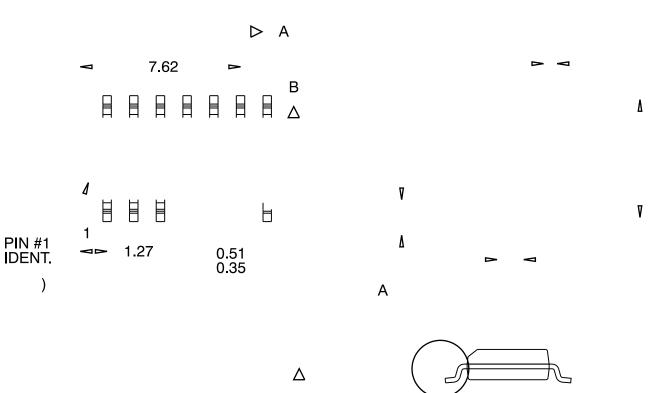

SOIC 14 NB CASE 751A-03 **ISSUE L**

### **DATE 03 FEB 2016**

- NOTES:

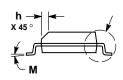

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

5. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- SIDE.

## **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code Α = Assembly Location

WL= Wafer Lot Υ = Year WW = Work Week G = Pb-Free Package

**STYLES ON PAGE 2**

### SOIC 14 CASE 751A-03 ISSUE L

DATE 03 FEB 2016

STYLE 7:

PIN 1. ANODE/CATHODE

2. COMMON ANODE

3. COMMON CATHODE

4. ANODE/CATHODE

5. ANODE/CATHODE

## SOIC14

0.10 (0.004)

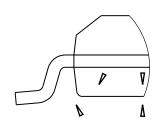

- - SEATING PLANE